PMC PMC-Sierra, Inc.

ISSUE 1

PM7325 ATLAS-3200

ATLAS-3200 PROGRAMMER'S GUIDE

PM7325

# **ATLAS-3200**

# 2488 MBIT/S SATURN USER NETWORK INTERFACE ATM LAYER SOLUTION

# **PROGRAMMER'S GUIDE**

CONFIDENTIAL PRELIMINARY ISSUE 1: DEC 2000

PM7325 ATLAS-3200

ISSUE 1

ATLAS-3200 PROGRAMMER'S GUIDE

# **PUBLIC REVISION HISTORY**

| lssue<br>No. | lssue<br>Date | Details of Change |

|--------------|---------------|-------------------|

| 1            | Dec 2000      | Document created. |

ISSUE 1

ATLAS-3200 PROGRAMMER'S GUIDE

# **CONTENTS**

| 1 | REFI                              | ERENCES                                | 1  |

|---|-----------------------------------|----------------------------------------|----|

| 2 | GLO                               | SSARY                                  | 2  |

| 3 | INTR                              | RODUCTION                              | 4  |

|   | 3.1                               | SCOPE                                  | 4  |

|   | 3.2                               | TARGET AUDIENCE                        | 4  |

|   | 3.3                               | NUMBERING CONVENTIONS                  | 5  |

|   | 3.4                               | PSEUDO-CODE CONVENTIONS                | 5  |

| 4 | ATLAS-3200 OVERVIEW6              |                                        |    |

|   | 4.1                               | SYSTEM APPLICATION EXAMPLE             | 7  |

|   | 4.2                               | OPERATION MODES                        | 8  |

|   | 4.3                               | DATA STRUCTURES                        | 10 |

| 5 | MICF                              | ROPROCESSOR INTERFACE                  | 15 |

|   | 5.1                               | MICROPROCESSOR INTERFACE BUS           | 15 |

|   | 5.2                               | REGISTER MEMORY MAP                    | 15 |

| 6 | PROGRAMMING HIGH LEVEL OPERATIONS |                                        |    |

|   | 6.1                               | ATLAS-3200 RESETTING                   |    |

|   |                                   | 6.1.1 ALGORITHM FOR HARDWARE RESETTING | 19 |

|   |                                   | 6.1.2 ALGORITHM FOR SOFTWARE RESETTING | 20 |

|   |                                   | 6.1.3 EXAMPLE ROUTINES                 | 20 |

|   | 6.2                               | ATLAS-3200 INITIALIZING                | 22 |

|   |                                   | 6.2.1 ALGORITHM                        | 23 |

|   |                                   | 6.2.2 CLOCK SETTINGS                   |    |

|     |        | ISSUE 1                      | ATLAS-3200 PROGRAMMER'S GUIDE |

|-----|--------|------------------------------|-------------------------------|

|     | 6.2.3  | OPERATION MODE SETTINGS      |                               |

|     | 6.2.4  | PHYSICAL INTERFACE SETTINGS. |                               |

|     | 6.2.5  | BACKWARDS CELL INTERFACE SE  | ETTINGS 28                    |

|     | 6.2.6  | CELL PROCESSOR SETTINGS      |                               |

|     | 6.2.7  | CELL COUNTING SETTINGS       |                               |

|     | 6.2.8  | POLICING SETTINGS            |                               |

|     | 6.2.9  | OAM SETTINGS                 |                               |

|     | 6.2.10 | SEARCH KEY SETTINGS          |                               |

|     | 6.2.11 | INTERRUPT SETTINGS           |                               |

|     | 6.2.12 | 2 VC TABLE SETTINGS          |                               |

| 6.3 | PHYS   | SICAL CONNECTION ADDING      |                               |

|     | 6.3.1  | ALGORITHM                    |                               |

|     | 6.3.2  | PHYSICAL ID MAPPING SETTINGS |                               |

|     | 6.3.3  | PER-PHY POLICING SETTINGS    |                               |

|     | 6.3.4  | SCALEABLE DATA QUEUE SETTIN  | GS 37                         |

|     | 6.3.5  | POLLING AND SERVICING CALENE | DAR SETTINGS 39               |

| 6.4 | PHYS   | SICAL CONNECTION REMOVAL     |                               |

|     | 6.4.1  | ALGORITHM                    |                               |

| 6.5 | VIRTU  | JAL CONNECTION ADDING        |                               |

|     | 6.5.1  | ADDING AN INDEPENDENT VCC    |                               |

|     | 6.5.2  | ADDING AN INDEPENDENT VPC    |                               |

|     | 6.5.3  | ADDING A VCC WITHIN A VPC    |                               |

|     | 6.5.4  | ALGORITHM                    |                               |

|     | 6.5.5  | VC TABLE CONFIGURATION SETTI | NGS                           |

|      |        | ISSUE 1                      | ATLAS-3200 PROGRAMMER'S GUIDE |

|------|--------|------------------------------|-------------------------------|

|      | 6.5.6  | VC TABLE ADDRESS SETTINGS    |                               |

|      | 6.5.7  | VC TABLE POLICING SETTINGS   | 53                            |

|      | 6.5.8  | VC TABLE OAM SETTINGS        | 55                            |

|      | 6.5.9  | PERFORMANCE MANAGEMENT SE    | TTINGS 56                     |

|      | 6.5.10 | EXAMPLE ROUTINES             | 56                            |

| 6.6  | VIRTU  | AL CONNECTION REMOVAL        | 61                            |

|      | 6.6.1  | ALGORITHM                    | 61                            |

|      | 6.6.2  | EXAMPLE ROUTINES             | 61                            |

| 6.7  | VIRTU  | AL CONNECTION SEARCH TREE M  | ODIFYING 63                   |

|      | 6.7.1  | SEARCH KEY SETTINGS          | 63                            |

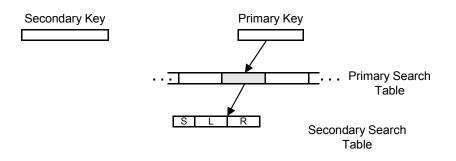

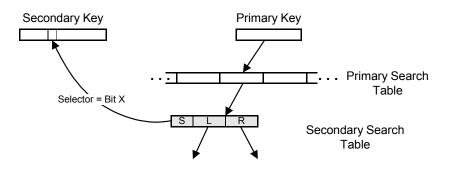

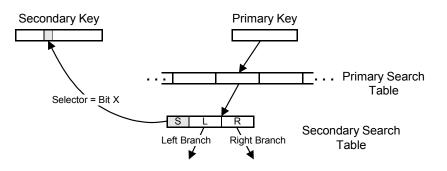

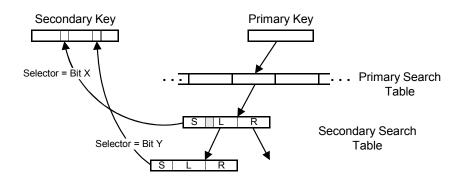

|      | 6.7.2  | SEARCH TREE STRUCTURE        | 65                            |

|      | 6.7.3  | ALGORITHM FOR FINDING A RECO | RD 68                         |

|      | 6.7.4  | ALGORITHM FOR INSERTING A RE | CORD71                        |

|      | 6.7.5  | ALGORITHM FOR REMOVING A RE  | CORD75                        |

|      | 6.7.6  | EXAMPLE ROUTINES             |                               |

| 6.8  | MICRO  | OPROCESSOR CELL INTERFACE CO | OMMUNICATING 97               |

|      | 6.8.1  | READING CELLS                |                               |

|      | 6.8.2  | WRITING CELLS                |                               |

| 6.9  | FIFO N | /ANAGING                     |                               |

|      | 6.9.1  | CHANGE OF STATE FIFO         |                               |

|      | 6.9.2  | COUNT ROLLOVER FIFO          | 102                           |

| 6.10 | INTER  | RUPT HANDLING                | 107                           |

| 6.11 | OAM C  | CELL PROCESSING              | 110                           |

|      | 6.11.1 | GENERAL OAM SETTINGS         |                               |

7

|      |        | ISSUE 1                      | ATLAS-3200 PROGRAMMER'S GUIDE |

|------|--------|------------------------------|-------------------------------|

|      | 6.11.2 | PROLT MANAGEMENT CELL PROC   | ESSING112                     |

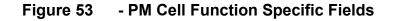

|      | 6.11.3 | PM CELL PROCESSING           | 116                           |

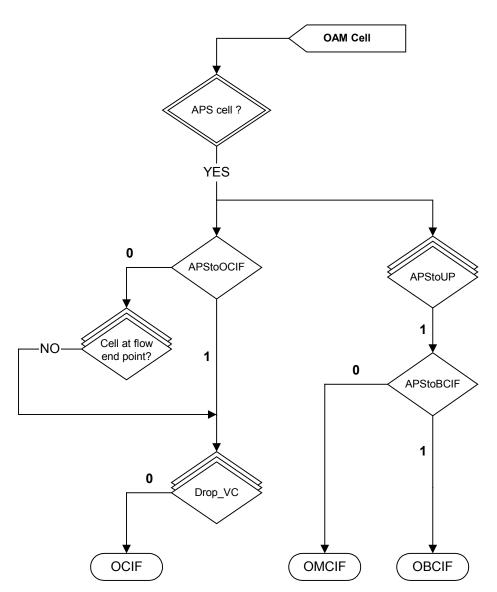

|      | 6.11.4 | APS CELL PROCESSING          | 123                           |

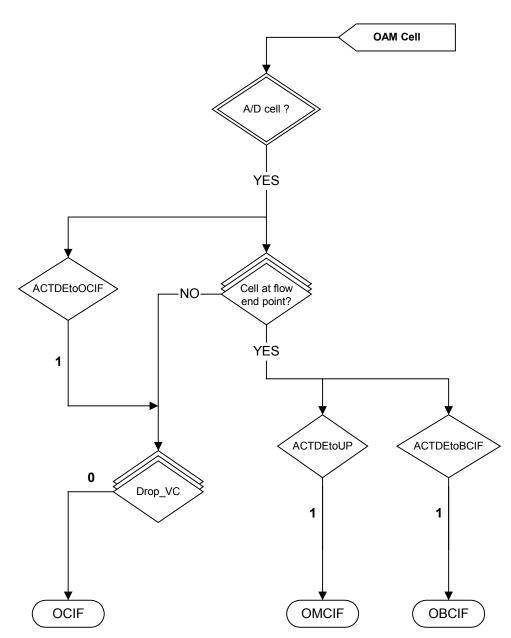

|      | 6.11.5 | ACTIVATION/DEACTIVATION CELL | PROCESSING 124                |

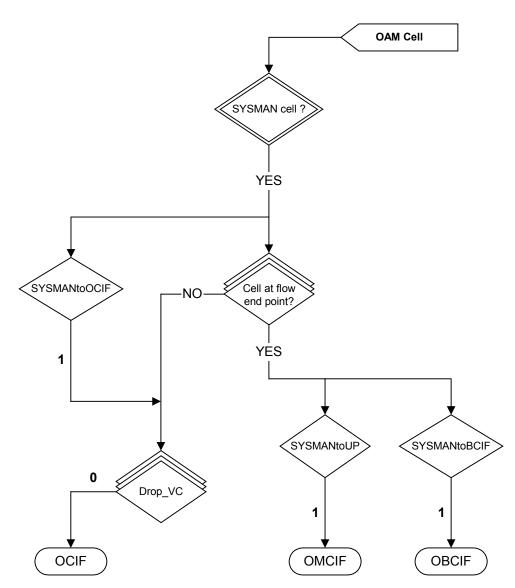

|      | 6.11.6 | SYSTEM MANAGEMENT CELL PRO   | DCESSING 124                  |

|      | 6.11.7 | RESOURCE MANAGEMENT CELL     | PROCESSING 124                |

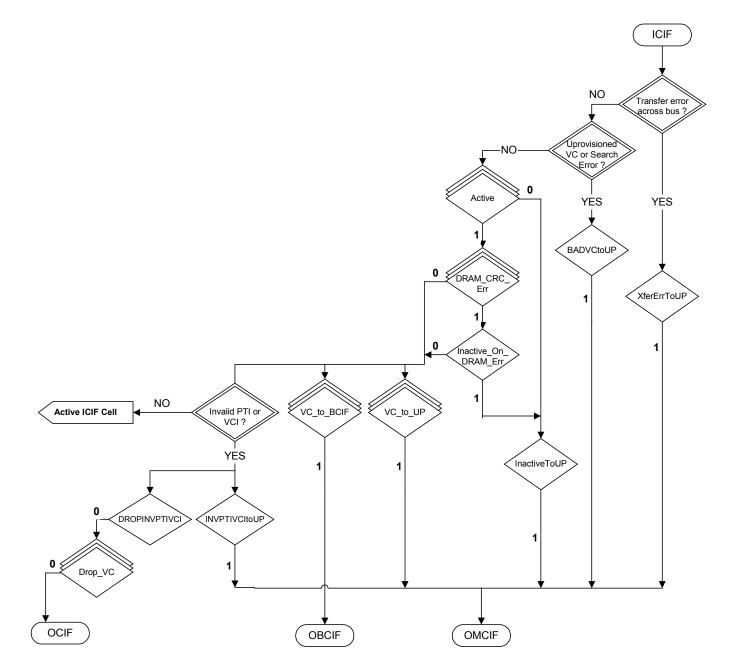

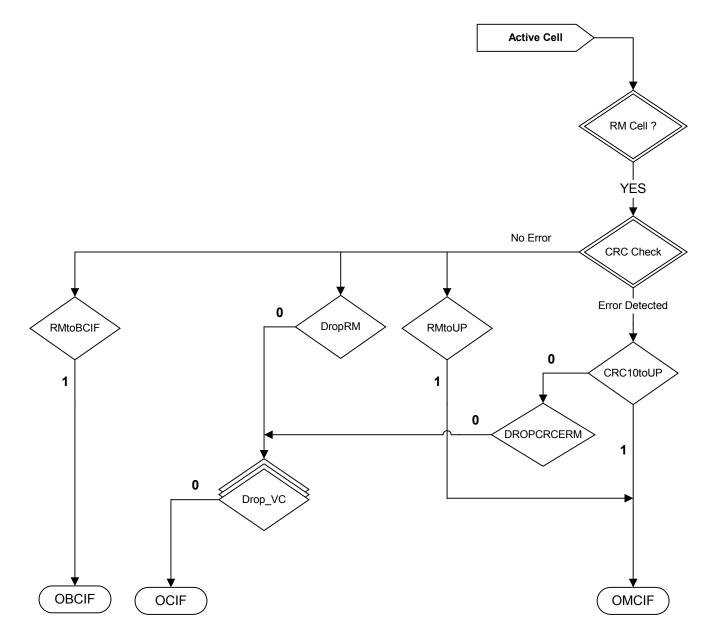

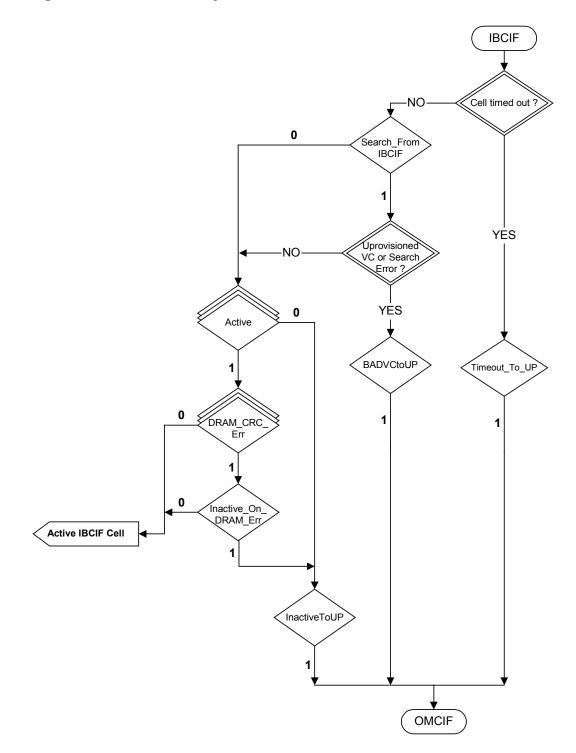

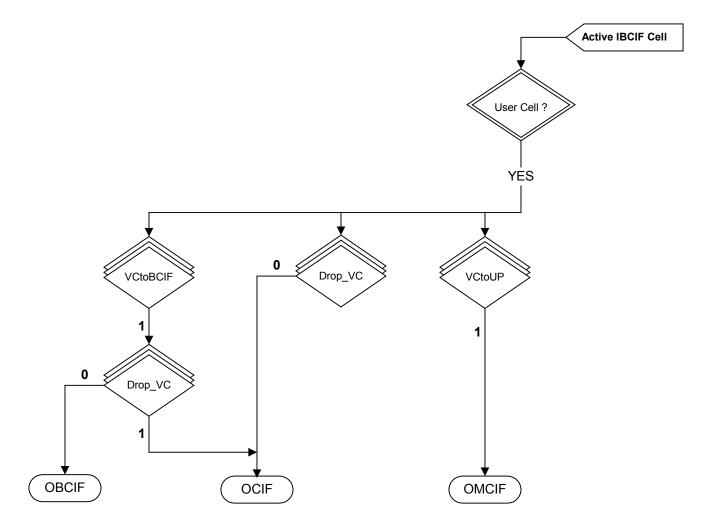

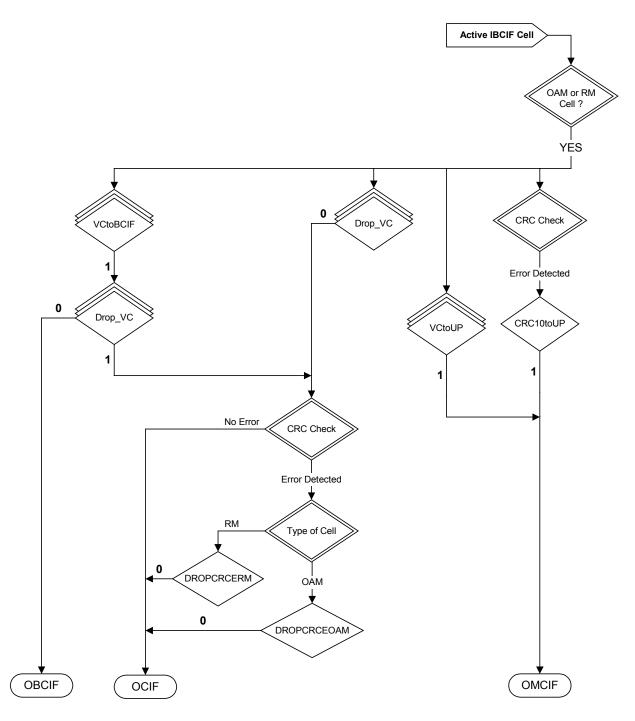

| 6.12 | CELL   | ROUTING                      |                               |

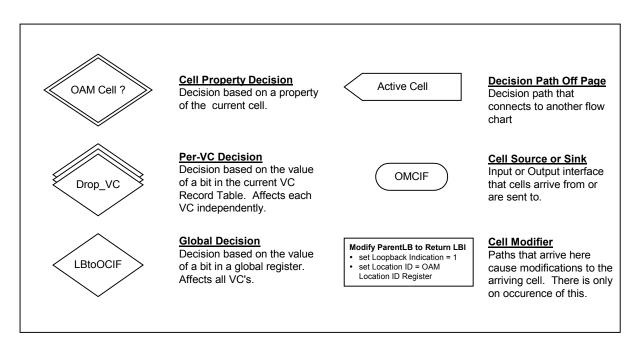

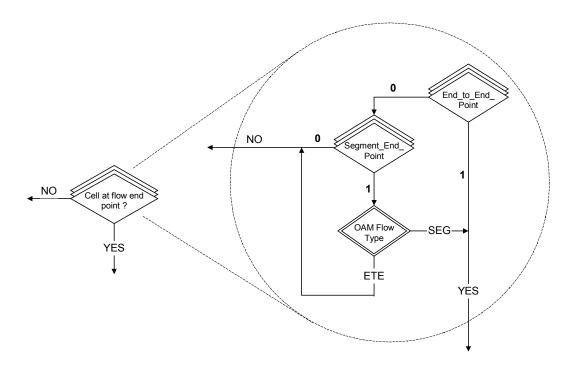

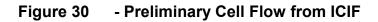

|      | 6.12.1 | FLOW CHART GUIDE             | 127                           |

|      | 6.12.2 | MCIF CELL ROUTING            | 130                           |

|      | 6.12.3 | BICIF CELL ROUTING           | 131                           |

|      | 6.12.4 | BCIF CELL ROUTING            |                               |

| PROC | GRAMN  | ING COMPONENT INTERFACES     |                               |

| 7.1  | DIRE   | CT REGISTER INTERFACING      | 149                           |

|      | 7.1.1  | READING                      |                               |

|      | 7.1.2  | WRITING                      |                               |

|      | 7.1.3  | EXAMPLE ROUTINES             | 149                           |

| 7.2  | EXTE   | RNAL SRAM INTERFACING        | 153                           |

|      | 7.2.1  | READING EXTERNAL SRAM ENTR   | IES 155                       |

|      | 7.2.2  | WRITING EXTERNAL SRAM ENTRI  | ES 155                        |

|      | 7.2.3  | DIAGNOSTIC TESTING           | 156                           |

|      | 7.2.4  | EXAMPLE ROUTINES             | 156                           |

| 7.3  | VC TA  | ABLE ENTRY INTERFACING       | 161                           |

|      | 7.3.1  | READING VC TABLE RECORDS     | 162                           |

|      |        |                              |                               |

| 1159 |      | ISSUE 1                          | ATLAS-3200 PROGRAMMER'S GUIDE |

|------|------|----------------------------------|-------------------------------|

|      |      | 7.3.3 EXAMPLE ROUTINES           |                               |

|      | 7.4  | SDQ ENTRY INTERFACING            |                               |

|      |      | 7.4.1 READING SDQ ENTRIES        |                               |

|      |      | 7.4.2 WRITING SDQ ENTRIES        |                               |

|      | 7.5  | PM TABLE RECORD INTERFACING .    | 171                           |

|      |      | 7.5.1 READING PM TABLE RECORD    | DS 173                        |

|      |      | 7.5.2 WRITING PM TABLE RECORD    | S 173                         |

|      | 7.6  | PHY ID MAPPING TABLE INTERFAC    | NG 175                        |

|      |      | 7.6.1 READING PHY ID MAPPING TA  | ABLE ENTRIES 176              |

|      |      | 7.6.2 WRITING PHY ID MAPPING TA  | ABLE ENTRIES 176              |

|      | 7.7  | PHY POLCING RAM INTERFACING      | 177                           |

|      |      | 7.7.1 READING PHY POLICING CON   | FIGURATION TABLES 178         |

|      |      | 7.7.2 WRITING PHY POLICING CON   | IFIGURATION TABLES 179        |

|      |      | 7.7.3 INITIALIZING PER-PHY POLIC | ING 180                       |

|      | 7.8  | PHY COUNT INTERFACING            |                               |

|      |      | 7.8.1 READING PER-PHY CELL COU   | JNTS 182                      |

|      |      | 7.8.2 WRITING PER-PHY CELL COU   | JNTS 183                      |

|      | 7.9  | CALENDAR ENTRY INTERFACING       |                               |

|      |      | 7.9.1 READING CALENDAR ENTRY     |                               |

|      |      | 7.9.2 WRITING CALENDAR ENTRY     |                               |

|      | 7.10 | MCIF INTERFACING                 |                               |

|      |      | 7.10.1 READING CELLS             | 190                           |

|      |      | 7.10.2 WRITING CELLS             | 190                           |

|      | 7.11 | CHANGE OF STATE FIFO INTERFAC    | ING 192                       |

8

9

|      | ISSUE 1                           | ATLAS-3200 PROGRAMMER'S GUIDE |

|------|-----------------------------------|-------------------------------|

|      | 7.11.1 READING COS ENTRIES        | 193                           |

| 7.12 | COUNT ROLLOVER FIFO INTERFACING   | 194                           |

|      | 7.12.1 READING CRO ENTRIES        | 195                           |

| PSEL | JDO-CODE REFERENCE                | 196                           |

| APPE | ENDIX A: OAM CELL DESCRIPTIONS    | 198                           |

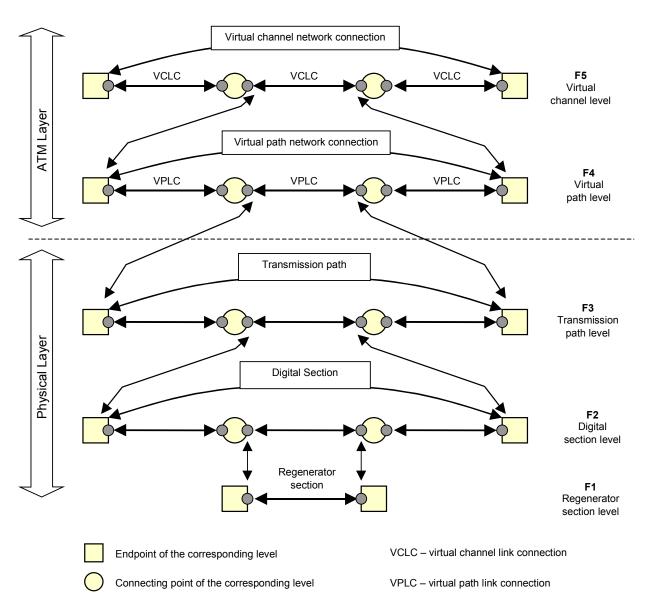

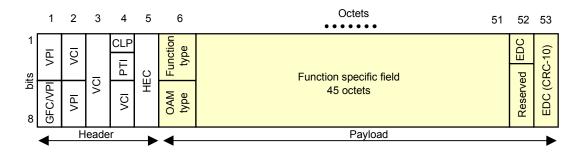

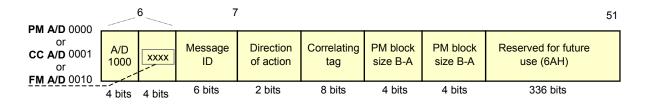

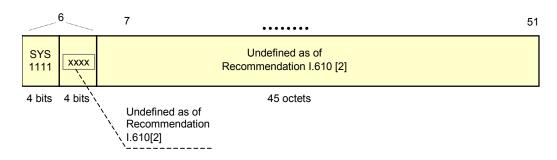

| 9.1  | GENERAL OAM CELL FORMAT           | 200                           |

| 9.2  | FAULT MANAGEMENT (FM) CELLS       | 203                           |

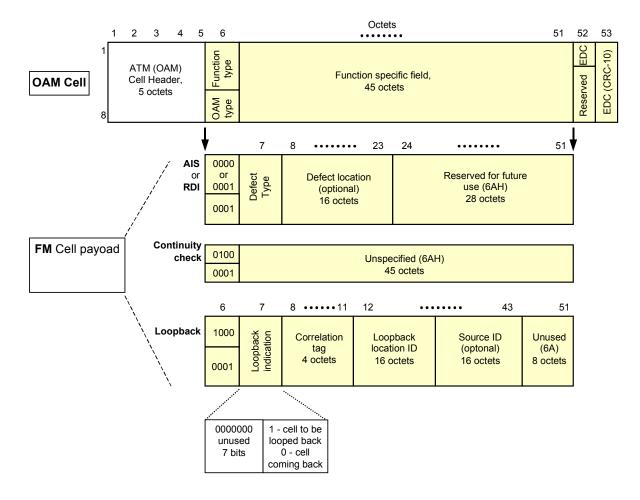

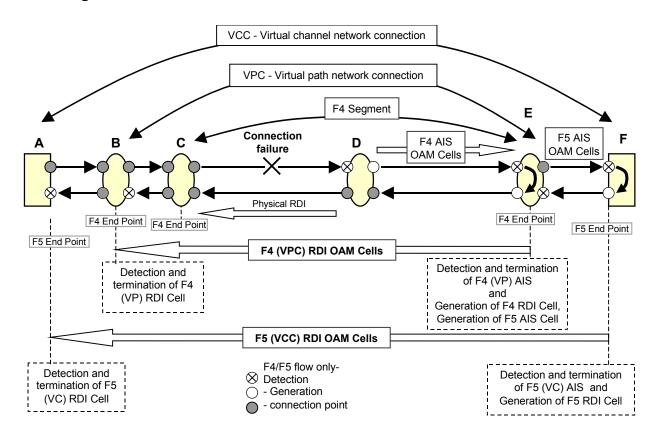

|      | 9.2.1 AIS AND RDI CELLS           | 203                           |

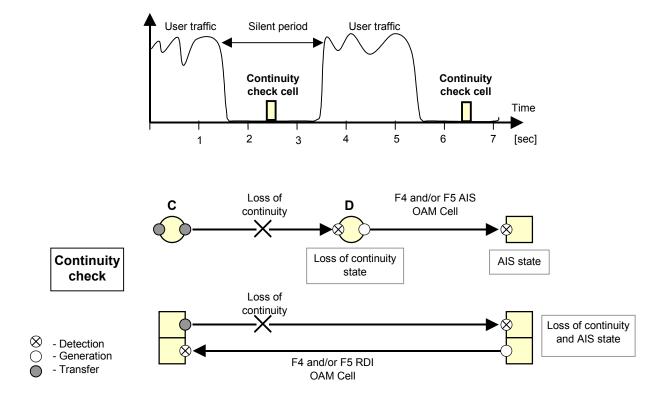

|      | 9.2.2 CC CELLS                    | 205                           |

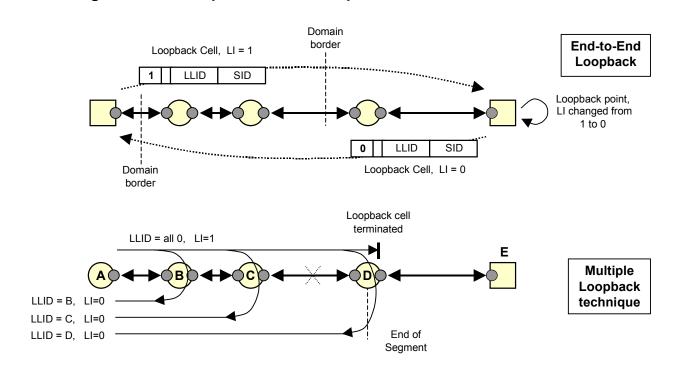

|      | 9.2.3 LOOPBACK CELLS              | 206                           |

| 9.3  | PERFORMANCE MANAGEMENT (PM) CE    | ELLS 207                      |

| 9.4  | ACTIVATE / DEACTIVATE (A/D) CELLS |                               |

| 9.5  | SYSTEM MANAGEMENT (SM) CELLS      |                               |

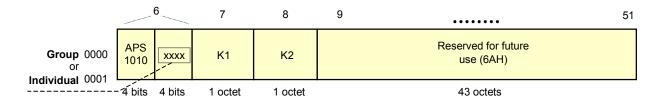

- 9.6 AUTOMATED PROTECTION SWITCHING (APS) CELLS .......211

PMC-Sierra, Inc.

ISSUE 1

# LIST OF FIGURES

| FIGURE 1 - ATLAS-3200 SYSTEM APPLICATION                     | 7    |

|--------------------------------------------------------------|------|

| FIGURE 2 - OPERATING MODE COMPONENTS AND DATA PATHS          | 9    |

| FIGURE 3 - VC RELATED DATA STRUCTURES                        | .11  |

| FIGURE 4 - FIFO DATA STRUCTURES                              | .11  |

| FIGURE 5 - MISCELLANEOUS DATA STRUCTURES                     | . 12 |

| FIGURE 6 - EXTERNAL SRAM PARTITIONING                        | . 13 |

| FIGURE 7 - REGISTER MAP                                      | . 16 |

| FIGURE 8 - RESET FLOW CHART                                  | . 18 |

| FIGURE 9 - INITIALIZATION FLOW CHART                         | 22   |

| FIGURE 10- VCC WITHIN VPC CONFIGURATION REQUIREMENTS         | 48   |

| FIGURE 11 - VCC WITHIN VPC SEARCH TREE EXAMPLE               | 49   |

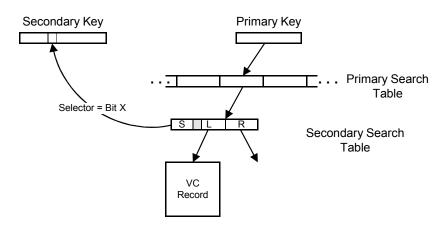

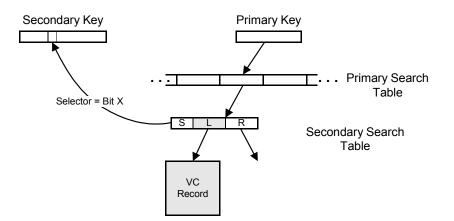

| FIGURE 12- SEARCH KEY CONSTRUCTION                           | 65   |

| FIGURE 13- SEARCH TREE STRUCTURE                             | 67   |

| FIGURE 14- SEARCH TREE FIND, STEP 2                          | 68   |

| FIGURE 15- SEARCH TREE FIND, STEP 3                          | 68   |

| FIGURE 16- SEARCH TREE FIND, STEP 4                          | 69   |

| FIGURE 17- SEARCH TREE FIND, STEP 5                          | 69   |

| FIGURE 18- SEARCH TREE FIND, STEP 6A                         | 70   |

| FIGURE 19- SEARCH TREE FIND, STEP 6B                         | 70   |

| FIGURE 20- SEARCH TREE FIND, STEP 7                          | . 71 |

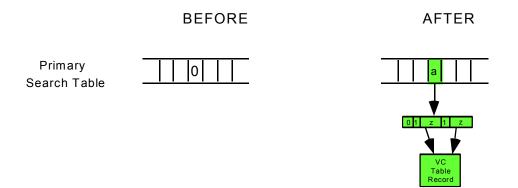

| FIGURE 21- SEARCH TREE INSERTION INTO AN EMPTY TREE          | 72   |

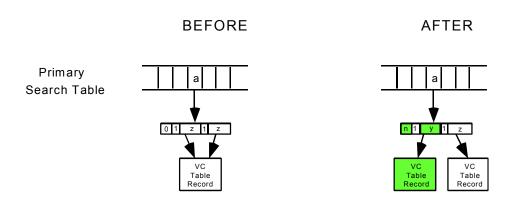

| FIGURE 22- SEARCH TREE INSERTION INTO A SINGLE RECORD TREE . | 73   |

ISSUE 1

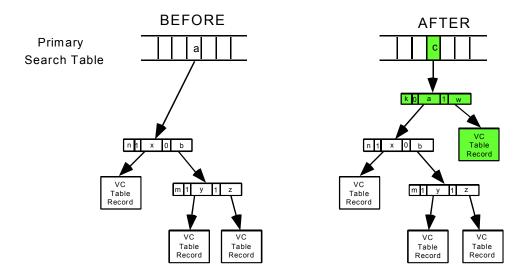

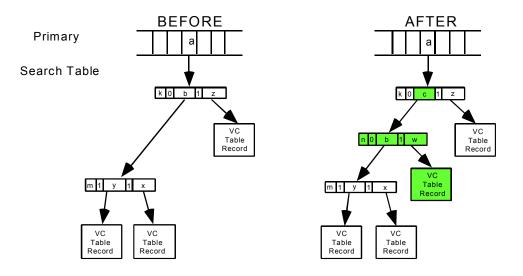

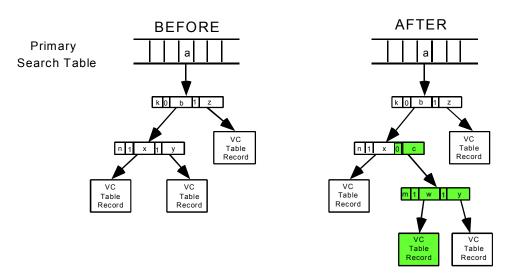

| FIGURE 23- SEARCH TREE INSERTION AT THE ROOT OF A TREE            |

|-------------------------------------------------------------------|

| FIGURE 24- SEARCH TREE INSERTION AT MIDDLE OF A TREE              |

| FIGURE 25- SEARCH TREE INSERTION AT LEAF                          |

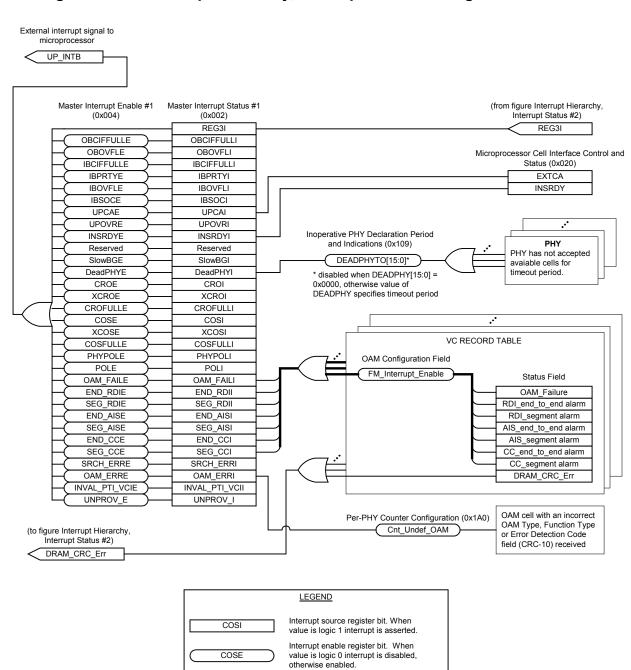

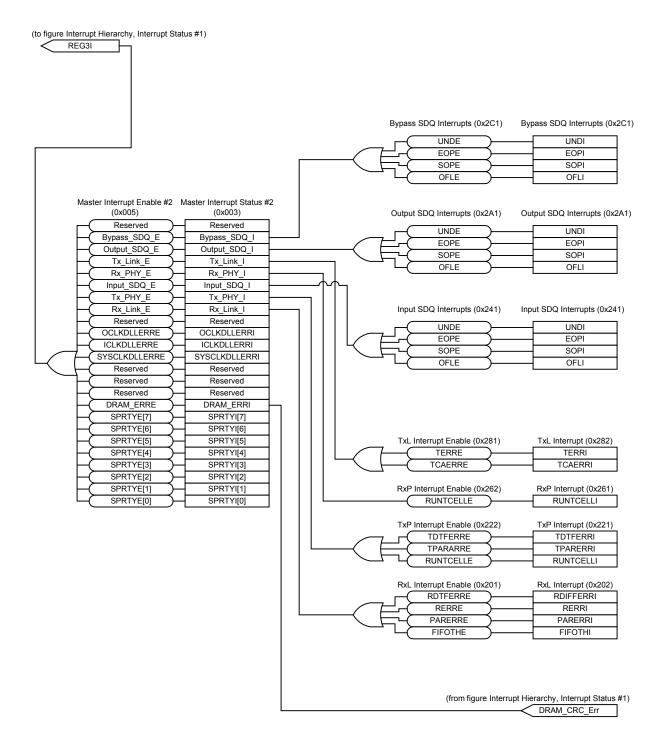

| FIGURE 26- INTERRUPT HIERARCHY, INTERRUPT STATUS #1 REG 108       |

| FIGURE 27- INTERRUPT HIERARCHY, INTERRUPT STATUS #2 REG 109       |

| FIGURE 28- CELL FLOW, LEGEND 127                                  |

| FIGURE 29- CELL AT FLOW END POINT SYMBOL 130                      |

| FIGURE 30- PRELIMINARY CELL FLOW FROM ICIF                        |

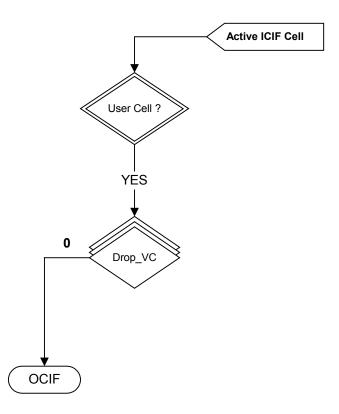

| FIGURE 31- USER CELL FLOW 132                                     |

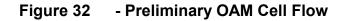

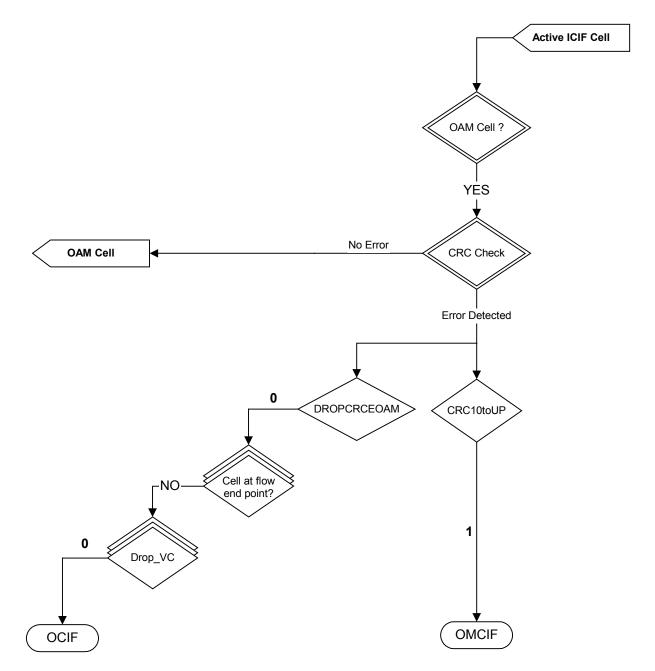

| FIGURE 32- PRELIMINARY OAM CELL FLOW 133                          |

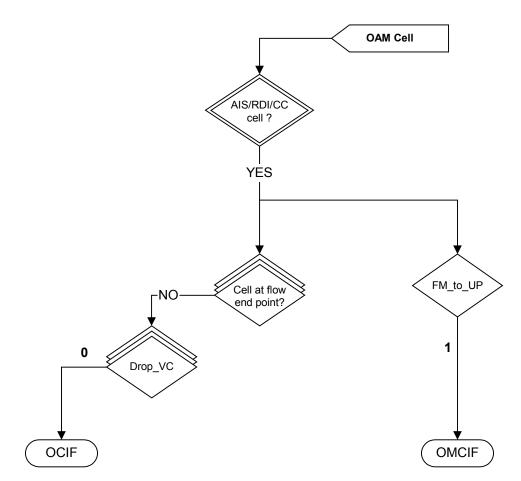

| FIGURE 33-AIS/RDI/CC CELL FLOW                                    |

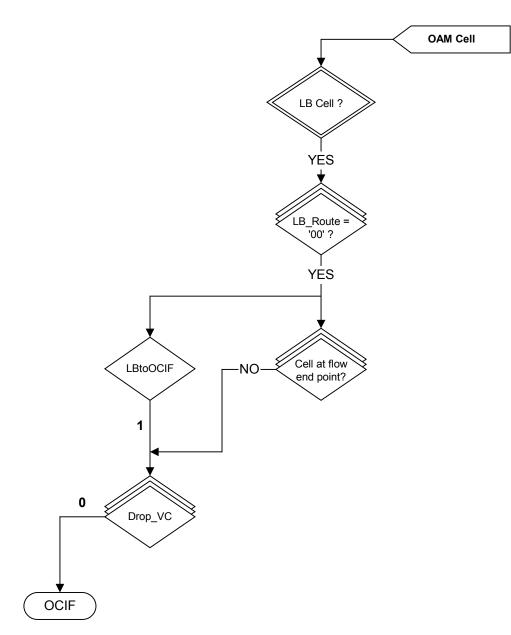

| FIGURE 34- LOOPBACK CELL FLOW, (LB_ROUTE = '00') 135              |

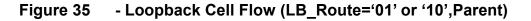

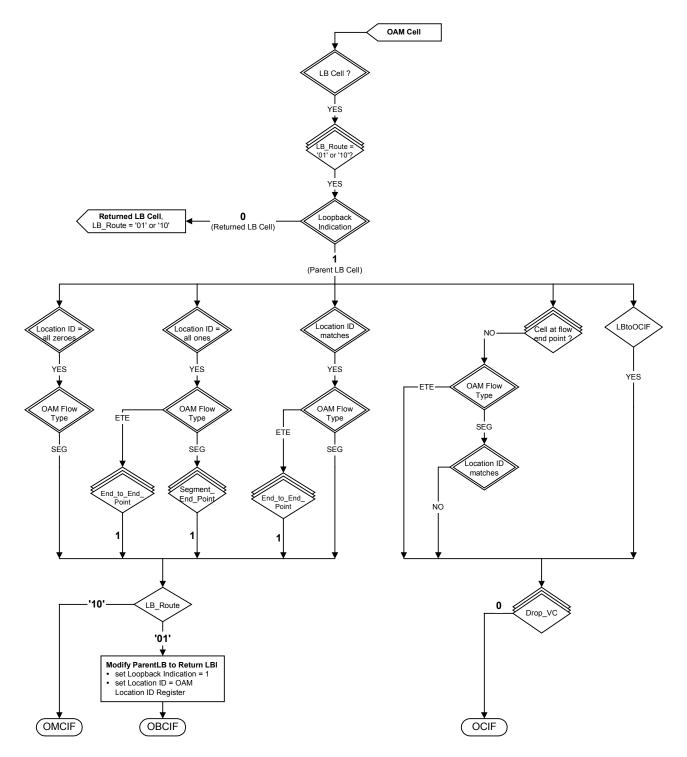

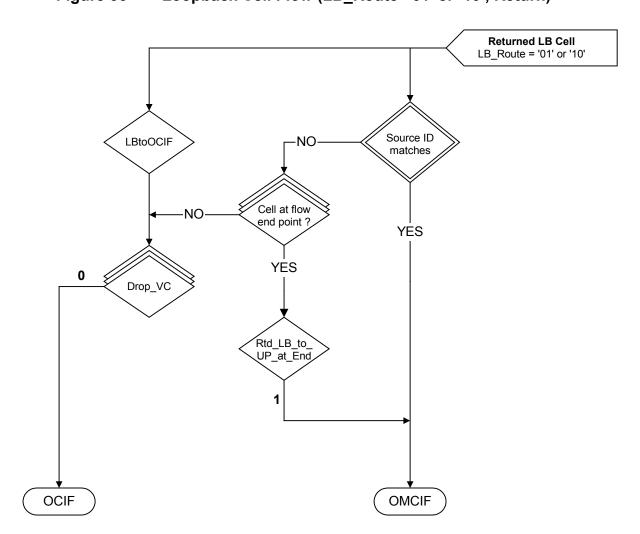

| FIGURE 35- LOOPBACK CELL FLOW (LB_ROUTE='01' OR '10', PARENT) 136 |

| FIGURE 36- LOOPBACK CELL FLOW (LB_ROUTE='01' OR '10', RETURN)137  |

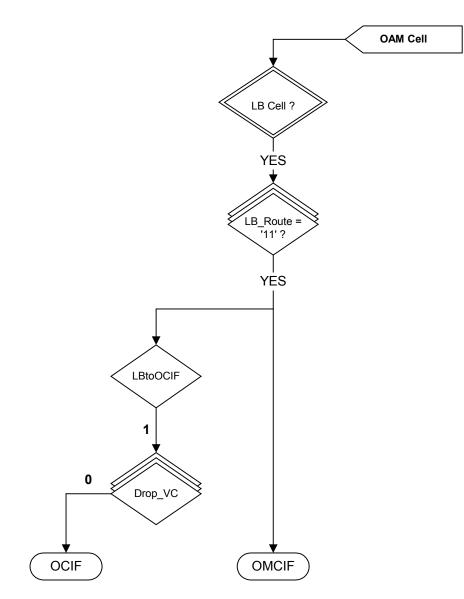

| FIGURE 37- LOOPBACK CELL FLOW, (LB_ROUTE = '11') 138              |

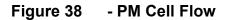

| FIGURE 38- PM CELL FLOW 139                                       |

| FIGURE 39-ACTIVATE/DEACTIVATE CELL FLOW                           |

| FIGURE 40- APS CELL FLOW 141                                      |

| FIGURE 41- SYSTEM MANAGEMENT CELL FLOW 142                        |

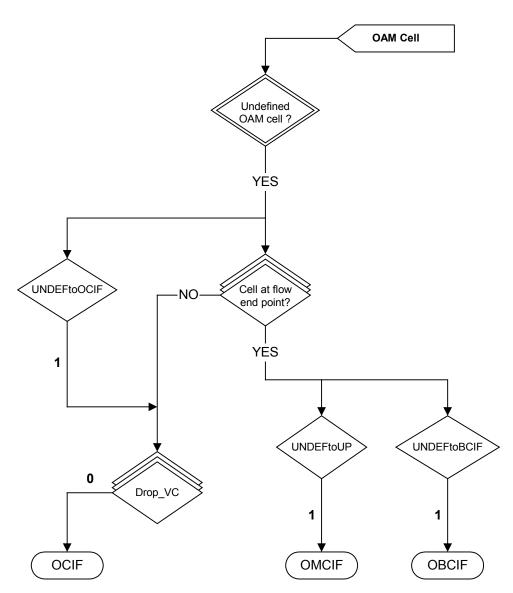

| FIGURE 42- OAM CELL FLOW 143                                      |

| FIGURE 43- RM CELL FLOW 144                                       |

| FIGURE 44- PRELIMINARY CELL FLOW FROM THE IBCIF 145               |

| FIGURE 45- USER CELL FLOW FROM THE IBCIF 146                      |

| FIGURE 46- OAM AND RM CELL FLOW FROM THE IBCIF                    |

| FIGURE 47- ATM OAM HIERARCHICAL LEVELS                     | 199  |

|------------------------------------------------------------|------|

| FIGURE 48- OAM CELL STRUCTURE                              | 200  |

| FIGURE 49- FM CELL FUNCTION SPECIFIC FIELDS                | 203  |

| FIGURE 50- AIS AND RDI FLOW                                | 204  |

| FIGURE 51- CC FLOW                                         | 206  |

| FIGURE 52- LOOPBACK FLOW EXAMPLES                          | 207  |

| FIGURE 53- PM CELL FUNCTION SPECIFIC FIELDS                | 208  |

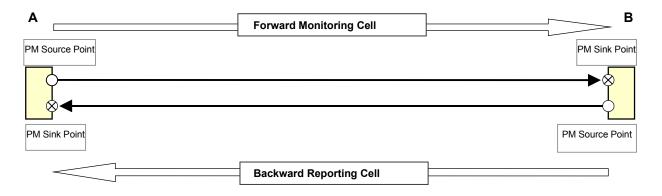

| FIGURE 54- EXAMPLE OF PM CELL FLOW                         | 209  |

| FIGURE 55- A/D CELL FUNCTION SPECIFIC FIELDS               | 210  |

| FIGURE 56- SYSTEM MANAGEMENT CELL FUNCTION SPECIFIC FIELDS | 5211 |

| FIGURE 57- APS CELL FUNCTION SPECIFIC FIELDS               | 211  |

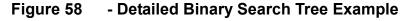

| FIGURE 58- DETAILED BINARY SEARCH TREE EXAMPLE             | 214  |

PMC-Sierra, Inc.

ISSUE 1

# LIST OF TABLES

| TABLE 1  | - TEST PIN CONNECTIONS 19                              |

|----------|--------------------------------------------------------|

| TABLE 2  | - TYPICAL MEMORY ACCESS TIMES IN STANDBY STATE 23      |

| TABLE 3  | - REGISTER BITS FOR PHYSICAL INTERFACE RESETTING 24    |

| TABLE 4  | - REGISTER BITS FOR SDQ AND BCIF RESETTING 24          |

| TABLE 5  | - REGISTER BITS FOR HALF SEC. CLOCK CONFIGURATION . 25 |

| TABLE 6  | - REGISTER BITS FOR OPERATION MODE SETTINGS            |

| TABLE 7  | - REGISTERS FOR PHYSICAL INTERFACE MODE CONFIG 27      |

| TABLE 8  | - REGISTERS FOR PHYSICAL CONNECTION PROCESSING 28      |

| TABLE 9  | - REGISTERS FOR BCIF CONFIGURATION                     |

| TABLE 10 | - CELL PROCESSOR CONFIG. REGISTER (0X100) 28           |

| TABLE 11 | - REGISTERS FOR CELL COUNTING CONFIGURATION            |

| TABLE 12 | - REGISTERS FOR POLICING CONFIGURATION                 |

| TABLE 13 | - REGISTERS FOR SEARCH KEY CONFIGURATION               |

| TABLE 14 | - REGISTERS FOR PER-PHY POLICING CONFIGURATION 36      |

| TABLE 15 | - SUGGESTED SDQ FIFO SIZES                             |

| TABLE 16 | - SDQ REGISTERS                                        |

| TABLE 17 | - POLLING AND SERVICING CALENDAR USE                   |

| TABLE 18 | - CALENDAR EXAMPLE: ONE STS-12 41                      |

| TABLE 19 | - CALENDAR EXAMPLE: ONE STS-12, ONE STS-3 41           |

| TABLE 20 | - CALENDAR EXAMPLE: ONE STS-12, TWO STS-3'S 41         |

| TABLE 21 | - REGISTERS FOR CALENDAR PROGRAMMING 42                |

| TABLE 22 | - VC TABLE RECORD, CONFIGURATION FIELD 50              |

| TABLE 23 - VC TABLE RECORD FIELDS FOR ADDRESSING SETTINGS 52     |

|------------------------------------------------------------------|

| TABLE 24 - VC RECORD FIELDS FOR POLICING SETTINGS                |

| TABLE 25       - GCRA AND GFR POLICING CONFIGURATIONS            |

| TABLE 26 - VC TABLE RECORD FIELDS FOR OAM SETTINGS               |

| TABLE 27 - SEARCH ENGINE CONFIG. REGISTER (0X10B) FIELDS 64      |

| TABLE 28 - SEARCH TABLE FIELD STRUCTURE                          |

| TABLE 29 - SEARCH TABLE FIELD DESCRIPTIONS       66              |

| TABLE 30 - REGISTERS FOR MCIF INDIRECT ACCESSING       97        |

| TABLE 31 - REGISTER BITS FOR COS FIFO INTERRUPTS 100             |

| TABLE 32 - REGISTER BITS FOR COS FIFO CONFIGURATION 100          |

| TABLE 33 - REGISTERS FOR COS FIFO INTERFACING                    |

| TABLE 34 - REGISTER BITS FOR CRO FIFO CONFIGURATION 103          |

| TABLE 35       - REGISTER BITS FOR CRO FIFO INTERRUPTS       106 |

| TABLE 36 - REGISTERS FOR CRO FIFO INTERFACING 106                |

| TABLE 37 - PER-VC GENERAL OAM SETTINGS       110                 |

| TABLE 38 - GLOBAL GENERAL OAM SETTINGS       111                 |

| TABLE 39 - PER-VC, FAULT MANAGEMENT SETTINGS                     |

| TABLE 40 - GLOBAL FAULT MANAGEMENT SETTINGS                      |

| TABLE 41 - REGISTERS FOR PM TABLE INDIRECT ACCESSING             |

| TABLE 42 - PM TABLE, CONFIG. AND STATUS FIELD                    |

| TABLE 43 - GLOBAL PERFORMANCE MANAGEMENT SETTINGS       120      |

| TABLE 44 - GLOBAL APS SETTINGS                                   |

| TABLE 45 - GLOBAL ACTIVATION/DEACTIVATION SETTINGS       124     |

| TABLE 46       - GLOBAL SYSTEM MANAGEMENT SETTINGS       124     |

|                                                                  |

| ISSUE 1 |  |

|---------|--|

| 10000   |  |

| TABLE 47       - GLOBAL RESOURCE MANAGEMENT SETTINGS               |  |

|--------------------------------------------------------------------|--|

| TABLE 48       - EXAMPLE CELL FLOW TO OCIF LOGIC CHART             |  |

| TABLE 49 - EXAMPLE CELL FLOW TO OMCIF LOGIC CHART                  |  |

| TABLE 50 - EXAMPLE CELL FLOW TO OBCIF LOGIC CHART 129              |  |

| TABLE 51 - REGISTERS FOR SRAM INDIRECT ACCESSING       153         |  |

| TABLE 52- SRAM ACCESS CONTROL REGISTER (0X10C)154                  |  |

| TABLE 53 - REGISTER BITS FOR SRAM CONFIG. AND INTERRUPTS 154       |  |

| TABLE 54         - REGISTERS FOR VC TABLE ENTRY INTERFACING        |  |

| TABLE 55 - VC TABLE ACCESS CONTROL REGISTER (0X111)       161      |  |

| TABLE 56 - REGISTERS FOR SDQ ENTRY INDIRECT PROGRAMMING . 167      |  |

| TABLE 57- SDQ INDIRECT ADDRESS REGS (0X244,0X2A4,0X2C4)167         |  |

| TABLE 58         - REGISTERS FOR PM TABLE INDIRECT ACCESSING       |  |

| TABLE 59 - PM WORD SELECT AND ACCESS CONTROL REG (0X170). 172      |  |

| TABLE 60 - REGISTERS FOR PHY MAP INDIRECT ACCESSING                |  |

| TABLE 61 - PHY INDIRECT ADDRESS REGISTER (0X209, 0X289) 175        |  |

| TABLE 62 - REGISTERS FOR PHY POLICING RAM INDIRECT ACCESS. 177     |  |

| TABLE 63 - PHY POLICING RAM ACCESS CONTROL REG (0X144) 177         |  |

| TABLE 64 - REGISTERS FOR PHY POLICING RAM INDIRECT ACCESS. 181     |  |

| TABLE 65 - PER-PHY COUNTER CONTROL REGISTER (0X1A1)                |  |

| TABLE 66 - REGISTERS FOR CALENDAR ENTRY ACCESS                     |  |

| TABLE 67 - CALENDAR ADDR. AND DATA REG.(0X20B, 0X265, 0X28B) . 184 |  |

| TABLE 68 - REGISTERS FOR MCIF INTERFACING                          |  |

| TABLE 69 - MCIF CONTROL AND STATUS REG(0X020) INSERT BITS 187      |  |

| TABLE 70- MCIF CONTROL AND STATUS REG(0X020) EXTRACT BITS. 189     |  |

|                                                                    |  |

ISSUE 1

| TABLE 71 - REGISTERS FOR COS FIFO INTERFACING              |

|------------------------------------------------------------|

| TABLE 72       - VC TABLE COS FIFO STATUS REGISTER (0X190) |

| TABLE 73 - REGISTERS FOR CRO FIFO INTERFACING       194    |

| TABLE 74       - VC TABLE CRO FIFO STATUS REGISTER (0X198) |

| TABLE 75    - F4 OAM CELL IDENTIFICATION                   |

| TABLE 76    - F5 OAM CELL IDENTIFICATION                   |

| TABLE 77 - OAM CELL TYPES AND FUNCTIONS       202          |

| TABLE 78 - EXAMPLE VC CHARACTERISTICS       212            |

| TABLE 79 - EXAMPLE SEARCH ENGINE CONFIG. REG. (0X10B) 212  |

ISSUE 1

ATLAS-3200 PROGRAMMER'S GUIDE

#### 1 REFERENCES

- 1. PMC-1990553, PMC-Sierra Inc., "OC-48 Saturn User Network Interface ATM Layer Solution Standard Product Data Sheet", Oct 2000, Issue 3

- 2. ITU-T Recommendation I.610 (02/1999), B-ISDN operation and maintenance principles and functions

- 3. ITU-T Recommendation I.630 (02/1999), ATM protection switching

- 4. ATM Forum TM4.1, ATM Forum Traffic Management Specification Version 4.1, 1999.

- 5. ITU-T Recommendation I.356 (03/00), B-ISDN ATM layer cell transfer performance

- 6. ITU-T Recommendation I.371 "Traffic Control and Congestion Control in B-ISDN", May, 1996

- 7. ATM Forum AF-TM-0121.000 Traffic Management Specification Version 4.1, March 1999

- 8. ITU-T Recommendation I.610 "B-ISDN Operation and Maintenance Principles and Functions", February 1999.

- 9. Bell Communications Research Generic Requirements for Operations of Broadband Switching Systems, GR-1248-CORE, Issue 3, August 1996.

- 10. ATM Forum AF-PHY-0136.000 UTOPIA 3 Physical Layer Interface, November 1999.

- 11. PMC-1980495, "POS-PHY Level 3: SATURN Compatible Interface for Packet Over SONET Physical Layer and Link Layer Devices", Issue 4, June 7, 2000.

- 12. ATM Forum AF-PHY-0039.000 UTOPIA, An ATM-PHY Interface Specification, Level 2, Version 1.0, June 1995.

- 13. PMC-880901 "Telecom System Block (TSB) User Manual", Issue 6, March 28, 1997.

PM7325 ATLAS-3200

ISSUE 1

ATLAS-3200 PROGRAMMER'S GUIDE

#### 2 GLOSSARY

| AIS   | Alarm Indication Signal. An OAM cell that indicates to downstream entities that there is a fault in the VC.                                                                              |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| СС    | Continuity Check. An OAM cell sent through the network so that downstream entities may differentiate between a failure and periods of low user cell traffic.                             |

| FM    | Fault Management. The mechanism used by the network to inform management entities and other network equipment of faults within the network. Consists of AIS, RDI, CC, and LB cell flows. |

| GCRA  | Generic Cell Rate Algorithm. The algorithm used to police<br>the cell transmission rate. Also known as the Leaky Bucket<br>Algorithm.                                                    |

| GFR   | Guaranteed Frame Rate. The algorithm used to police the packet transmission rate.                                                                                                        |

| IBCIF | Input Backwards Cell Interface. A component of the ATLAS-<br>3200 that receives cells from another ATLAS-3200 that is<br>transmitting in the opposite direction.                         |

| ICIF  | Input Cell Interface. A component of the ATLAS-3200 that receives cells.                                                                                                                 |

| IMCIF | Input Microprocessor Cell Interface. A component of the ATLAS-3200 that receives cells or packets from the microprocessor and inserts them into a connection.                            |

| OAM   | Operations and Maintenance. The maintenance of VCs within the network.                                                                                                                   |

| OBCIF | Output Backwards Cell Interface. A component of the ATLAS-3200 that outputs cells to another ATLAS-3200 that is transmitting in the opposite direction.                                  |

| OCIF  | Output Cell Interface. A component of the ATLAS-3200 that outputs cells.                                                                                                                 |

| OMCIF | Output Microprocessor Cell Interface. A component of the ATLAS-3200 that receives cells or packets from a connection and sends them to the microprocessor.                               |

| PRELIMINARY<br>PROGRAMMER'S GUIDE | PMC-Sierra, li                                                                                                                                         | nc. <b>PM7325 ATLAS-3200</b>                                                    |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| PMC-2001159                       | ISSUE 1                                                                                                                                                | ATLAS-3200 PROGRAMMER'S GUIDE                                                   |

| PM                                | Performance Management. The network to monitor the performation particular VC.                                                                         | 2                                                                               |

| RDI                               | Remote Defect Indication. An C<br>entity at the OAM flow endpoint<br>fault in the VC.                                                                  | •                                                                               |

| SDQ                               | Scaleable Data Queue. A mem that is configurable into variable the input and output interfaces.                                                        | 5                                                                               |

| VC                                | Virtual Connection. This refers<br>Connection (VPC) or a Virtual C                                                                                     |                                                                                 |

| VCC                               | Virtual Channel Connection. A two network elements. A virtual normally a constituent member where the VPC consists of one sometimes known as an F5 con | channel connection is<br>of a virtual path connection,<br>or more VCCs. This is |

| VPC                               | Virtual Path Connection. A virtu<br>network elements. A virtual path<br>or more physical links. This is s<br>connection.                               | h connection may span one                                                       |

ISSUE 1

ATLAS-3200 PROGRAMMER'S GUIDE

# 3 INTRODUCTION

This document is a guide to programming the software for a microprocessor that interfaces to an ATLAS-3200 chip. It is intended to ease the integration of the ATLAS-3200 into system designs and to enable optimum performance to be achieved. Suggested programming algorithms, configuration settings and discussion of the chip's operation are presented.

The document's major sections are an overview of the ATLAS-3200, a description of the microprocessor interface, a high level programming section, and a component interface programming section. The Programming High Level Operations section discusses configuration settings and algorithms related to programming the high level functionality of the ATLAS-3200. The Programming Component Interfaces section provides the algorithms for reading and writing each of the ATLAS-3200 interfaces.

#### 3.1 Scope

The ATLAS-3200 Programmer's Guide supplements the ATLAS-3200 Data Sheet [1] with additional information for software programming.

Typical system applications will use more than one ATLAS-3200, however, due to the variety of possible configurations this document only discusses software programming for a single chip. Programming the routines to coordinate multiple ATLAS-3200s must be done on an application specific basis.

Although every effort has been taken to ensure the consistency between this document and the ATLAS-3200 Data Sheet [1], some discrepancies may occur. In case of inconsistencies between this document and the ATLAS-3200 Data Sheet [1], the information in the Data Sheet [1] should be considered accurate and takes precedence over information provided in this document.

Please contact a PMC-Sierra Applications Engineer for information not covered in this document.

#### 3.2 Target Audience

This document is prepared for software and system designers who are using the ATLAS-3200 chip. Some prior knowledge of the ATM protocol, as well as some knowledge of the C programming language and computer operation is necessary to fully understand this document.

#### 3.3 Numbering Conventions

The following numbering conventions are used throughout this document:

- Decimal 129, 6, 12

- Binary 011, 1011 (when distinguished from decimal by the context)

or 0b011, 0b1011

• Hexadecimal 0x1FE2

#### 3.4 Pseudo-Code Conventions

The pseudo-code in this document is shown in a C-like syntax. The pseudo-code segments are provided as a reference in order to understand a particular procedure or concept. The pseudo-code, however, is not compile-ready and is not provided for all sections. The pseudo-code segments are contained in the Example Routines sections at the end of the major sections to which they relate.

Function calls that are made to other pseudo-code routines that are defined in this document are highlighted in bold. Function calls that are not highlighted in bold indicate that the routine is not provided. The routines that are not provided are either self explanatory or application specific.

ATLAS-3200 PROGRAMMER'S GUIDE

# 4 ATLAS-3200 OVERVIEW

The ATLAS-3200 is an integrated circuit that implements ATM Layer functions that include header translation, cell rate policing, per-connection cell counting and I.610 compliant OAM requirements for up to 64K virtual connections. It is a uni-directional part that is intended to be situated between the physical layer devices and the traffic manager.

The sections below discuss a typical system application, the operating modes, and the data structures. These sections are intended to serve as a reference for general understanding of the ATLAS-3200, and are referred to frequently in the rest of the document.

ATLAS-3200 PROGRAMMER'S GUIDE

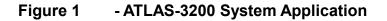

# 4.1 System Application Example

A typical system application is shown in Figure 1. The ATLAS-3200s are typically used in pairs. One chip of the pair receives cells/packets from PHY Layer devices and sends them towards the traffic manager/switch core. This chip is said to be in Ingress mode. The other chip of the pair receives cells/packets from the traffic manager/switch core and sends them to the PHY Layer devices. This chip is said to be in Egress mode. The Backwards Cell Interfaces allow the ATLAS-3200s to insert cells into the opposite direction cell flow. Each ATLAS-3200 has an external SRAM bank for holding part of the connection information (the other part being held in the internal embedded DRAM) and a Microprocessor Interface to provide the connection to a microprocessor. This document is a guide to programming the software for this microprocessor.

PRFI IMINARY

PMC-2001159

PROGRAMMER'S GUIDE

ATLAS-3200 PROGRAMMER'S GUIDE

#### 4.2 Operation Modes

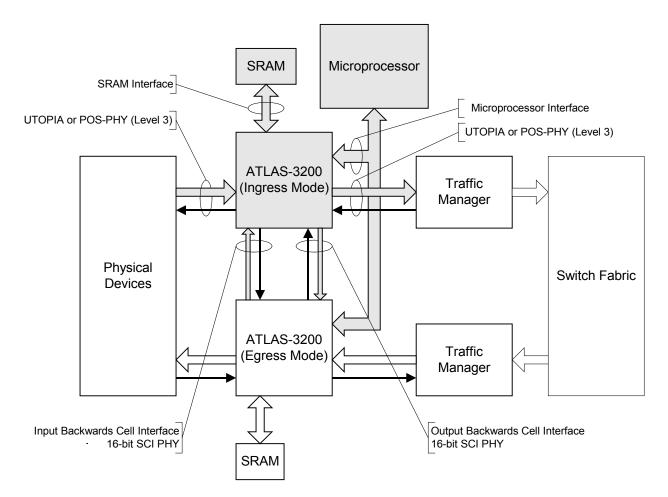

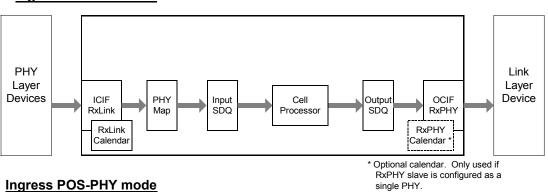

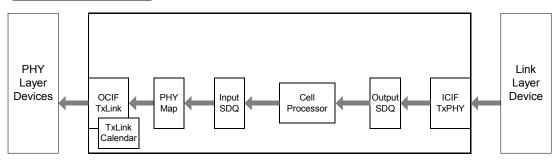

The ATLAS-3200 can be configured in four Operating Modes based on the signaling type and the direction of cell transmission with respect to the switch core. The signaling type can be either UTOPIA or POS-PHY, and the transmission direction can be either Ingress or Egress. UTOPIA Level 3 is used for transferring fixed-length ATM cells; and POS-PHY Level 3 is used for transferring variable-length packets. Applications that require the ATLAS-3200 to transfer mixed cell and packet traffic should use POS-PHY signalling.

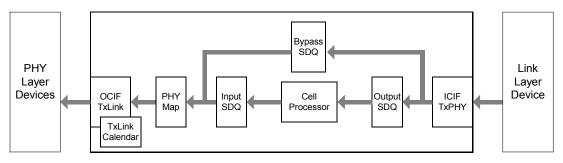

In each operating mode different components and data paths within the ATLAS-3200 are used. A diagram summarizing each operating mode is provided in Figure 2.

All the programming routines in this document for a single ATLAS-3200, however, they apply equally to all modes of operation (Ingress or Egress and UTOPIA or POS-PHY) unless noted otherwise.

# Figure 2 - Operating Mode Components and Data Paths

#### Ingress UTOPIA mode

PRELIMINARY

PMC-2001159

PROGRAMMER'S GUIDE

#### Bypass SDQ PHY Link Layer Layer Devices Device OCIF ICIF PHY Input Cell Output RxLink Мар SDQ Processor SDQ RxPHY **RxPHY** Calendar

#### Egress UTOPIA mode

#### Egress POS-PHY mode

ISSUE 1

#### 4.3 Data Structures

The ATLAS-3200's operation relies on data structures located in internal and external memory. One bank of external SRAM stores the VC Linkage Table and Search Tables. All other data structures are stored in memory internal to the ATLAS-3200.

The microprocessor can access all data structures indirectly through these registers. The indirect access interface to each data structure is described in Section 7 Programming Component Interfaces. The figures in this section show all the data structures that are accessible by the microprocessor.

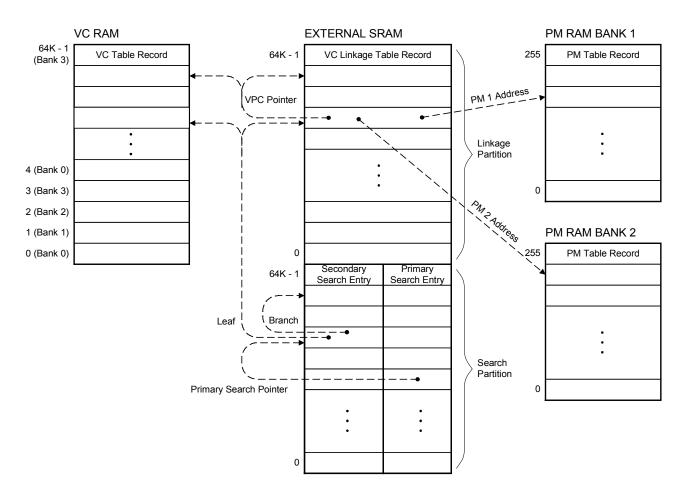

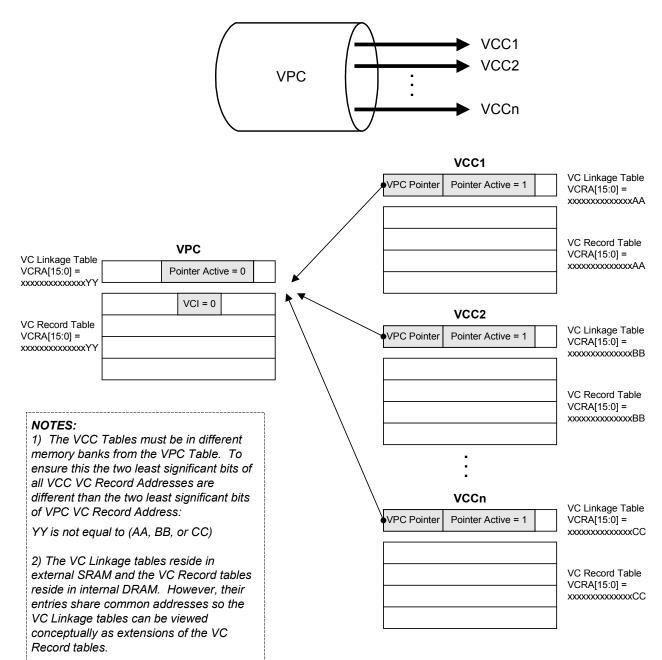

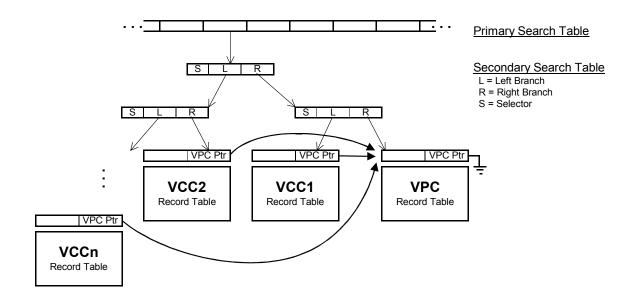

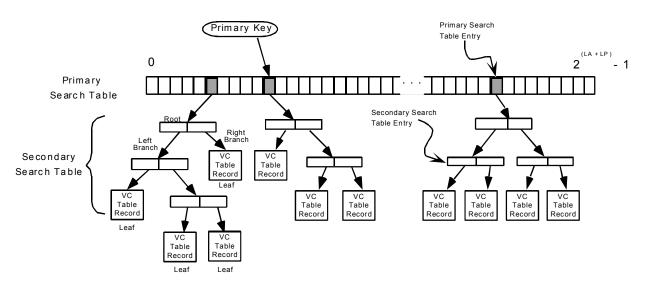

Figure 3 shows the memory locations and relationships between the data structures directly related to the Virtual Connection Record Tables. The dashed lines in Figure 3 indicate fields in the data structures that point to other locations in memory. One example of each pointer type is shown. The VC Linkage Table should be viewed conceptually as an extension of the VC Table, but resides in external SRAM instead of the internal DRAM for performance reasons. Thus, the information in location 0x123 (for example) of the linkage table is simply an extension of the information in location 0x123 of the VC Table.

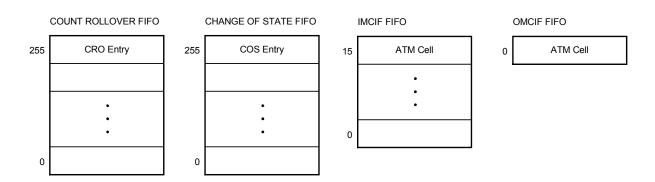

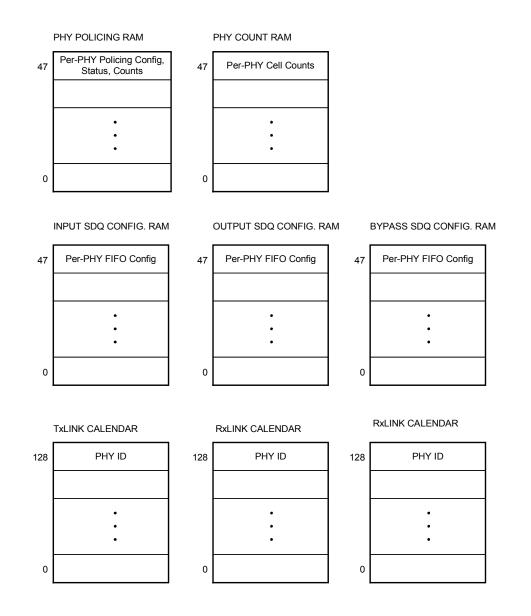

The FIFOs contained in the ATLAS-3200 are shown in Figure 4, and all the remaining internal data structures are shown in Figure 5.

A description of the external memory sizing is shown in Figure 6.

ISSUE 1

ATLAS-3200 PROGRAMMER'S GUIDE

# Figure 4 - FIFO Data Structures

ISSUE 1

PRELIMINARY

PMC-2001159

PROGRAMMER'S GUIDE

ATLAS-3200 PROGRAMMER'S GUIDE

# Figure 5 - Miscellaneous Data Structures

ISSUE 1

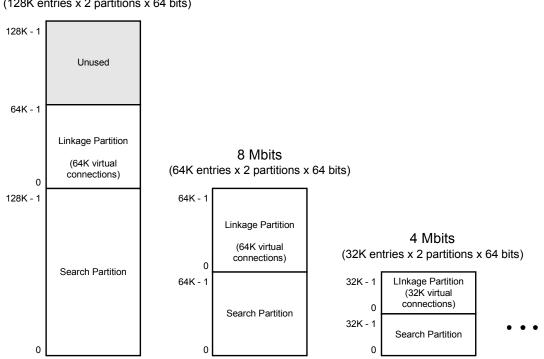

The size of the external SRAM can be varied to suit application specific requirements. The SRAM is always divided into a Linkage Partition and a Search Partition, which can support a maximum of 64K Linkage entries and 128K Search entries. In Figure 3, the SRAM shown is 8 Mbits (64K entries x 2 partitions x 64 bits). The partitioning configuration for various SRAM sizes is described below and shown in Figure 6.

- An 8 Mbit SRAM is the minimum size required to allow a full set of 64K virtual connections (one VC for each VC Linkage Table Record), and provides 64K Search entries.

- A 16 Mbit SRAM also allows 64K virtual connections but increases the number of Search entries to the maximum of 128K. The additional size of the Search Partition allows the full VCI-VPI-PHYID address to be resolved and eases the maintenance of the search table by providing extra room for modifications.

- Any SRAM smaller than 8 Mbits may be used with the number of allowed virtual connections decreasing proportionally.

#### Figure 6 - External SRAM Partitioning

16 Mbits (128K entries x 2 partitions x 64 bits)

PM7325 ATLAS-3200

PRELIMINARY PROGRAMMER'S GUIDE PMC-2001159

ISSUE 1

ATLAS-3200 PROGRAMMER'S GUIDE

When accesses are made to the SRAM through indirect registers, the microprocessor specifies which partition it wishes to access, and the address within the partition beginning at an offset of 0. The use of these partitions relies on the hardware connection between the MSB of the SRAM address bus and the MSB of the ATLAS-3200 SRAM address bus (SADDR[17]).

# 5 MICROPROCESSOR INTERFACE

**ISSUE 1**

The ATLAS-3200 has a generic microprocessor programming interface that provides access to a set of registers through the microprocessor interface bus. All microprocessor control and data transfer operations are performed through these registers. The sections below discuss the signals on the microprocessor interface bus and the direct registers.

#### 5.1 Microprocessor Interface Bus

Microprocessor accesses to the ATLAS-3200 involve the 11-bit address bus (UP\_ADDR[11:0]) that selects a register to be accessed and the 32-bit bidirectional data bus (UP\_DAT[31:0]) over which data is transferred.

The busy signal (UP\_BUSYB) is asserted while a microprocessor initiated access to external or internal RAM data is pending. The microprocessor can use this signal for polling or interrupt driven waiting. BUSY bits corresponding to each memory block are also accessible in the internal registers.

The DMA request signal (UP\_DMAREQ) is asserted when the Output Microprocessor Cell Interface (OMCIF) contains a cell to be read. This signal can be polled by the microprocessor to check for arriving cells at the OMCIF. The interrupt signal (UP\_INTB) can also be configured to indicate cell arrivals if an interrupt driven approach is used.

The interrupt request signal (UP\_INTB) indicates when an unmasked interrupt source is active. The Interrupt Status registers must be read in order to identify the specific interrupt request source.

The chip select (UP\_CSB), write (UP\_WRB), read (UP\_RDB) and address strobe (UP\_ALE) signals are used for standard asynchronous read and write cycles as described in the Data Sheet [1].

The reset signal (UP\_RSTB) performs a hard reset to the ATLAS-3200 when it is set low.

#### 5.2 Register Memory Map

A memory map of the direct registers that are available to the microprocessor are listed in Figure 7. During typical operation only the Normal Mode Registers will be accessed. See the Data Sheet[1] for a comprehensive list of the Normal Mode Registers.

PM7325 ATLAS-3200

ATLAS-3200 PROGRAMMER'S GUIDE

# Figure 7 - Register Map

# 6 PROGRAMMING HIGH LEVEL OPERATIONS

This section contains guides to programming the major functional operations that will typically be performed on the ATLAS-3200. Programming algorithms, register configurations, explanations ATLAS-3200 operations, and some example pseudo-code are provided.

# 6.1 ATLAS-3200 Resetting

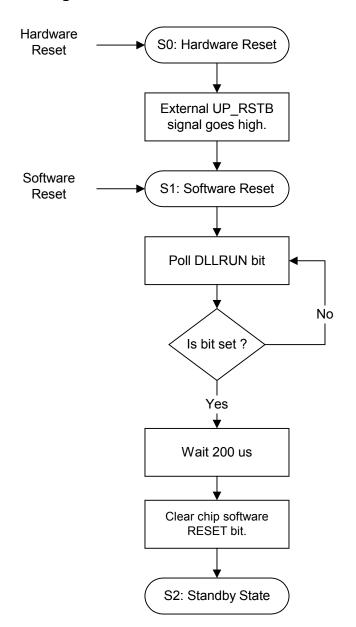

This section describes the ATLAS-3200's state transitions between the Hardware Reset, Software Reset and Standby states. A summary of the reset state transitions is shown in Figure 8. The algorithms to perform hardware and software resets are discussed in the sections below.

Figure 8 - Reset Flow Chart

#### Hardware Reset State:

The hardware reset state is entered when the UP\_RSTB input pin is forced low. This state has the following characteristics:

- Internal registers (0x000 0xFFF) are reset to their default states.

- Digital outputs are tri-stated.

- All internal ATLAS-3200 components are in low-power, stand-by mode.

#### Software Reset State:

The Software Reset state is automatically entered after a hardware reset is removed or it can be entered by setting the RESET bit in the Master Reset and Configuration Register (0x000). This state has the following characteristics:

- Internal registers (0x000 0xFFF) are reset to their default states.

- Digital outputs are NOT tri-stated. The ATLAS-3200 is in Ingress Pos-PHY that is the state in which all UL3/POS pins that can be either inputs or outputs, are inputs. This avoids contention on startup.

- Generic Microprocessor Programming Interface and the DLL Clock are operational. All other internal ATLAS-3200 components in low-power, stand-by mode.

#### 6.1.1 Algorithm for Hardware Resetting

The following steps need to be taken to proceed to the Software Reset state. The procedure to perform these steps will rely on the specific hardware implementation and may not be under microprocessor control.

1. Set up external signals. Ensure that the JTAG test pins are connected as listed in Table 1

| Pin Name | Value |

|----------|-------|

| ТСК      | 0     |

| TMS      | 0     |

| TDI      | 0     |

| TRSTB    | 1     |

#### Table 1 - Test Pin Connections

2. Take the ATLAS-3200 out of hardware reset by forcing the UP\_RSTB pin high.

### 6.1.2 Algorithm for Software Resetting

The following steps need to be taken to proceed to the Standby state. These steps are performed by the microprocessor through the Generic Microprocessor Programming Interface.

- If this state was entered from the Hardware Reset state then leave the RESET bit in the Master Reset and Configuration Register (0x000) set to logic 1, and wait for the DLLRUN bit in the Master Clock Monitor Register (0x006) to be set to logic 1 for at least 200 us. This ensures that the SYSCLK DLL has been locked for sufficient time to allow the embedded DRAM to initialize.

- 2. Take the ATLAS-3200 out of software reset by writing a 0 to the RESET bit in the Master Reset and Configuration Register (0x000). Note that each of the components will still be held in reset by their individual RESET bits.

### 6.1.3 Example Routines

#### 6.1.3.1 resetDevice

This function forces a software reset then brings the ATLAS-3200 into its standby state.

Inputs: (none)

Outputs: (none)

#### Pseudocode:

ISSUE 1

ATLAS-3200 PROGRAMMER'S GUIDE

BTMSK\_MASTER\_CFG\_AND\_RST\_RESET)

```

wait for 200us

```

return }

ATLAS-3200 PROGRAMMER'S GUIDE

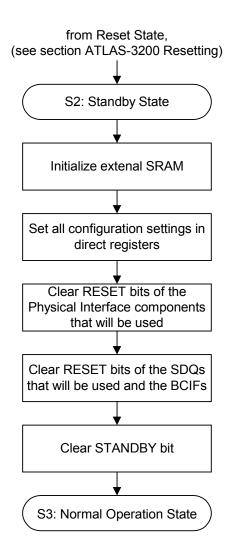

# 6.2 ATLAS-3200 Initializing

This section is a guide to programming the initialization routines for the ATLAS-3200. Initialization will typically be performed once after a reset. A summary of the initialization state transitions is shown in Figure 9.

Initializing the ATLAS-3200 involves setting the operational parameters for all the internal components to prepare them for Normal Operation state. The initialization should be performed while in Standby sate. Once initialization is complete the ATLAS-3200 can be brought into Normal Operation state. The sections below discuss the initialization algorithm and descriptions of all of the component settings that need to be initialized.

# Figure 9 - Initialization Flow Chart

ATLAS-3200 PROGRAMMER'S GUIDE

#### Standby State:

The Standby state is automatically entered after a software reset is removed or it can be entered from the Normal Operation state by setting the STANDBY bit in the Master Reset and Configuration Register (0x000).

The Standby state has the following characteristics:

- Cell Processor is disabled. The processing of cells currently in the pipeline is completed, but no more cells are accepted. This prevents passing corrupted cells while initializing the ATLAS-3200.

- All ATLAS-3200 components except the Cell Processor are enabled.

- All internal bus cycles are available for external SRAM and internal DRAM access (i.e. access to the Search Tables, VC Linkage Table and VC Table is given highest priority and no other processing will interrupt the SRAM and DRAM busses). The typical access times are given in Table 2.

Table 2

- Typical Memory Access Times in Standby State

| Memory Location | Standby State    | Normal Operation State |

|-----------------|------------------|------------------------|

| External SRAM   | 5 SYSCLK cycles  | 22 SYSCLK cycles       |

| Internal DRAM   | 25 SYSCLK cycles | 220 SYSCLK cycles      |

#### 6.2.1 Algorithm

The algorithm to initialize the ATLAS-3200 is as follows:

- 1. Ensure the ATLAS-3200 is in Standby state by checking that the STANDBY bit in the Master Reset and Configuration Register (0x000) is set to logic 1.

- IMPORTANT: Write logic 1 to both the SRAM\_BUSY\_EN bit and DRAM\_BUSY\_EN bit in the Master Reset and Configuration Register (0x000). These bits must be set to 1 to enable the BUSY bits that are used to access all the indirect data structures. The default values of both the SRAM\_BUSY\_EN bit and DRAM\_BUSY\_EN are logic 0, so they must be changed after each reset.

- 3. Clear the external SRAM by writing zeroes to all memory locations.

ATLAS-3200 PROGRAMMER'S GUIDE

- 4. Configure the global settings for all the internal components. The following sections provide the detailed setting descriptions for each component. Note that only the direct registers are accessable now since the components still have their individual reset bits set following the chip reset.

- 5. Clear the reset bits for the two Physical Interface components that will be used in the desired operating mode. The different operating modes are shown in Figure 2. See Table 3 for a list of the physical interface reset bits.

| Bit Name | Register                  | Operating Mode |

|----------|---------------------------|----------------|

| RXLRST   | RxL Configuration (0x200) | Ingress        |

| RXPRST   | RxP Configuration (0x260) | Ingress        |

| TXLRST   | TxL Configuration (0x280) | Egress         |

| TXPRST   | TxP Configuration (0x220) | Egress         |

#### Table 3 - Register Bits for Physical Interface Resetting

6. Clear the reset bits for the SDQ components that will be used in the desired operating mode and the Backwards Cell Interface. The different operating modes are shown in Figure 2. See Table 4 for list of the reset bits. It is important that the SDQs are brought out of reset **after** the physical interfaces have been configured. This is because the Pre/Post Lengths in the physical in configuration registers propagate to the SDQs when they are activated.

| Table 4 | - Register Bits for SDQ and BCIF Resetting |

|---------|--------------------------------------------|

|---------|--------------------------------------------|

| Bit Name | Register                                                 | Operating Mode  |

|----------|----------------------------------------------------------|-----------------|

| SDQRST   | Input SDQ Control (0x240)                                | Pos-Phy, Utopia |

| SDQRST   | Output SDQ Configuration (0x2A0)                         | Pos-Phy, Utopia |

| SDQRST   | Bypass SDQ Configuration (0x2C0)                         | Pos-Phy         |

| IBCIFRST | Input Backwards Cell Interface<br>Configuration (0x030)  | (all)           |

| OBCIFRST | Output Backwards Cell Interface<br>Configuration (0x038) | (all)           |

Bring the ATLAS-3200 from Standby state into Normal Operation state by writing a logic 0 to the STANDBY bit in the Master Reset and Configuration Register (0x000).

ATLAS-3200 PROGRAMMER'S GUIDE

#### 6.2.2 Clock Settings

During the Reset state any changes to the default Delay Locked Loop clock configurations should have been made (see section 6.1 ATLAS-3200 Resetting). The remaining clock to configure is the Half Second Clock which is used as a trigger for OAM alarm monitoring. This is done by setting the GEN\_HALFSECCLK bit in the Cell Processing Configuration Register (0x100) according to Table 5.

Table 5

- Register Bits for Half Sec. Clock Configuration

| Bit Name       | Register                                             | Description                                                                                                                                                 |

|----------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GEN_HALFSECCLK | Cell Processing<br>Configuration<br>Register (0x100) | <ul> <li>0: External signal<br/>HALFSECCLK is used.</li> <li>1: Clock is derived internally<br/>from SYSCLK.<br/>HALFSECCLK input is<br/>unused.</li> </ul> |

To check that all the clocks are running use the following procedure:

- 1. Read the Master Clock Monitor Register (0x006). This will clear the clock active bits.

- 2. Wait longer than the length of the longest clock period which is 500ms of the HALFSECCLOCK

- 3. Read the Master Clock Monitor Register (0x006) and check that all of the clock active bits have been set. This will confirm that the clocks are functioning.

# 6.2.3 Operation Mode Settings

After a reset the ATLAS-3200 defaults to the Ingress, Pos-PHY mode which is the state in which all POS/UL3 pins that can be either inputs or outputs, are inputs. This avoids external bus contention on startup.

Select the desired operation mode according to Table 6.

ATLAS-3200 PROGRAMMER'S GUIDE

#### Table 6 - Register Bits for Operation Mode Settings

| Bit Name        | Register                                          | Desc | cription                          |

|-----------------|---------------------------------------------------|------|-----------------------------------|

| Egress_IngressB | Master Configuration                              |      | Ingress mode.                     |

|                 | and Reset (0x000)                                 |      | RxLink and RxPHY blocks are used. |

|                 |                                                   | 1    | Egress mode.                      |

|                 |                                                   |      | TxPHY and TxLink blocks are used. |

| POS_UL3B        | DS_UL3B Master Configuration<br>and Reset (0x000) |      | Utopia Level 3 signaling.         |

|                 |                                                   |      | POS-PHY 3 signaling.              |

# 6.2.4 Physical Interface Settings

The operation of the ATLAS-3200's physical interface depends on which operating mode it is in: Ingress/Egress and POS-PHY/Utopia. The registers that need to be programmed for each operating mode are shown shaded in Table 7. Unused registers do not need to be programmed.

ISSUE 1

ATLAS-3200 PROGRAMMER'S GUIDE

# Table 7- Registers for Physical Interface Mode Config.

| Register             | Address | Ingre   | ss     | Egre    | SS     | Description                                                                               |

|----------------------|---------|---------|--------|---------|--------|-------------------------------------------------------------------------------------------|

|                      |         | POS-PHY | Utopia | POS-PHY | Utopia |                                                                                           |

| RxL Configuration    | 0x200   |         |        |         |        | Reset bit and configuration settings                                                      |

| RxL Data Type Field  | 0x20C   |         |        |         |        | Identification words used to identify<br>incoming data as either ATM cells<br>or packets. |

| RxL Interrupt Enable | 0x201   |         |        |         |        | Interrupt enables for the RxL<br>Interrupt Register (0x202).                              |

| RxP Configuration    | 0x260   |         |        |         |        | Reset bit and configuration settings.                                                     |

| RxP Data Type Field  | 0x266   |         |        |         |        | Identification words inserted to<br>outgoing ATM cells or packets.                        |

| RxP Interrupt Enable | 0x262   |         |        |         |        | Interrupt enables for the RxP<br>Interrupt Register (0x261).                              |

| TxP Configuration    | 0x220   |         |        |         |        | Reset bit and configuration settings                                                      |

| TxP Data Type Field  | 0x223   |         |        |         |        | Identification words used to identify<br>incoming data as either ATM cells<br>or packets. |

| TxP Interrupt Enable | 0x222   |         |        |         |        | Interrupt enables for the TxP<br>Interrupt Register (0x221).                              |

| TxL Configuration    | 0x280   |         |        |         |        | Reset bit and configuration settings                                                      |

| TxL Data Type Field  | 0x28C   |         |        |         |        | Identification words inserted to<br>outgoing ATM cells or packets.                        |

| TxL Interrupt Enable | 0x281   |         |        |         |        | Interrupt enables for the TxL<br>Interrupt Register (0x282).                              |

The RxL, RxP, TxP, and TxL interfaces each have a reset bit in their Configuration registers. Before programming any of the configuration settings for a given interface, the interface's reset bit must be set. Once all the registers have been programmed the reset bit can be cleared.

In each Physical Interface mode the ATLAS-3200 supports 48 physical devices. The ATLAS-3200 may be configured to pass some physical connections transparently. This feature is typically used when cells from a certain PHY are to be processed in another device, such as another ATLAS-3200. This allows multiple Atlas-3200s to be cascaded, each handling cells from some of the PHY's. By default after a reset all physical connections will be processed. If it is desired that some physical connections not be processed, set the registers listed in Table 8 as required.

ATLAS-3200 PROGRAMMER'S GUIDE

#### Table 8 - Registers for Physical Connection Processing

| Register                       | Address | Description                                            |

|--------------------------------|---------|--------------------------------------------------------|

| Per-PHY Processing<br>Enable 1 | 0x105   | Process enable bits for physical connections 0 to 31.  |

| Per-PHY Processing<br>Enable 2 | 0x106   | Process enable bits for physical connections 31 to 47. |

# 6.2.5 Backwards Cell Interface Settings

The configuration of the Backwards Cell Interface is contained in the registers listed in Table 9. See the Data Sheet [1] for detailed descriptions of these registers. When programming the registers, the reset bits in the corresponding Configuration register must first be set before proceeding. Once the registers have been programmed the reset bits can be cleared.

#### Table 9 - Registers for BCIF Configuration

| Register                                                       | Address | Description                                                         |

|----------------------------------------------------------------|---------|---------------------------------------------------------------------|

| Input Backwards Cell<br>Interface Configuration                | 0x030   | IBCIF reset bit and configuration settings.                         |

| Output Backwards Cell<br>Interface Configuration               | 0x038   | OBCIF reset bit and configuration settings.                         |

| Backward Cell Interface<br>Pacing and Head of Line<br>Blocking | 0x104   | Cell interval and timeout settings. See Data Sheet [1] for details. |

# 6.2.6 Cell Processor Settings

The general operation of the cell processor is controlled by the Cell Processor Configuration Register (0x100) that contains the configuration bits listed in Table 10. For detailed descriptions of these settings see the Data Sheet [1] and other sections of this Programming Guide referenced in Table 10.

#### Table 10 - Cell Processor Config. Register (0x100)

| Bit   | Name   | Description                                                  |

|-------|--------|--------------------------------------------------------------|

| 31:29 | Unused | Always set to logic 0 when writing. Read value is undefined. |

PMC-Sierra, Inc.

PM7325 ATLAS-3200

ISSUE 1

ATLAS-3200 PROGRAMMER'S GUIDE

| Bit | Name                    | Description                                                                   |

|-----|-------------------------|-------------------------------------------------------------------------------|

| 28  | Copy_FwPM_Timesta<br>mp | (see 6.11.3 PM Cell Processing)                                               |

| 27  | GEN_HALFSECCLK          | (see section 6.2.2)                                                           |

| 26  | F4SAISF5EAIS            | (see 6.11.2 Fault Management Cell                                             |

| 25  | F4SAISF5ERDI            | Processing)                                                                   |

| 24  | F4EAISF5EAIS            |                                                                               |

| 23  | F4EAISF5SRDI            |                                                                               |

| 22  | ForceCC                 |                                                                               |

| 21  | AUTO_AIS                |                                                                               |

| 20  | COS_DRAM_ERR_EN         | (see Section 6.9.1 Change of State FIFO)                                      |

| 19  | Reserved                | Always set to logic 0 when writing. Read value is undefined.                  |

| 18  | COS_Fail_EN             | (see Section 6.9.1 Change of State FIFO)                                      |

| 17  | COS_FAIL_ONLY           |                                                                               |

| 16  | COS_EN                  |                                                                               |

| 15  | Sat_Fast_PM_Counts      | (see Section 6.9.2 Count Rollover FIFO.)                                      |

| 14  | CRO_FIFO_EN             |                                                                               |

| 13  | Alternate_Count         | 0: Arriving cells increment Cell Count fields in all VC Table Records         |

|     |                         | 1: Arriving cells increment Alternate Count fields in all VC Table Records.   |

| 12  | VP_RM_PTI6              | 0: VPC (F4) Resource Management cells identified by VCI=6 and PTI is ignored. |

|     |                         | 1: VPC (F4) Resource Management cells identified by VCI=6 and PTI=110.        |

| 11  | Search_Verify_En        | (see 6.7 Virtual Connection Search Tree Modifying)                            |

| 9   | SRAM_Even_Parity        | (see Section 7.2 External SRAM)                                               |

ATLAS-3200 PROGRAMMER'S GUIDE

| Bit | Name              | Description                                                                                                                                                                                                                     |

|-----|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ы   | INAILIE           | Description                                                                                                                                                                                                                     |

| 8   | Cell_Info_to_OCIF | Enables insertion of Cell Information into<br>outgoing cells routed to the OCIF. This<br>information is for the convenience of an ASIC<br>or tester, to assist in identifying the cell and<br>the connection from which it came |

| 7   | Timeout_To_UP     | Controls routing of cells that timeout while waiting to be inserted from the IBCIF. See Section 0 for details.                                                                                                                  |

| 6   | Reserved          | Always set to logic 0 when writing. Read value is undefined.                                                                                                                                                                    |

| 5   | Cell_Info_To_UP   | Enables insertion of Cell Information into<br>cells routed to the MCIF. This information is<br>to assist in identifying the cell type and the<br>reason why it was routed to the MCIF.                                          |

| 4   | XGFC              | Controls insertion of translated fields into                                                                                                                                                                                    |

| 3   | XUDF              | outgoing cells.                                                                                                                                                                                                                 |

| 2   | XHEC              |                                                                                                                                                                                                                                 |

| 1   | XPREPO            |                                                                                                                                                                                                                                 |

| 0   | XVPIVCI           |                                                                                                                                                                                                                                 |

#### 6.2.7 Cell Counting Settings

The ATLAS-3200 supports per-VC and per-PHY cell counting. The cell counting configuration registers are listed in Table 11. These registers should typically be set during initialization, however, they can also be re-configured during Normal Operation state.

The per-VC cell counts are stored in fields in the VC Table Records. The Cell Counting Configuration Register specifies on a global basis, which type of cells are counted in the per-VC counts. Program the Cell Counting Configuration Register as required for the application.

The per-PHY cell counts are stored in Per-PHY Counter Memory (see Figure 5) and are accessed through indirect registers. The Per-PHY Counter Configuration Register specifies on a global basis which type of cells are counted in the per-PHY counts. Program the Per-PHY Counter Configuration Register as required for the application.

ATLAS-3200 PROGRAMMER'S GUIDE

#### Table 11 - Registers for Cell Counting Configuration

| Register                                  | Address | Description                                                                               |

|-------------------------------------------|---------|-------------------------------------------------------------------------------------------|

| Cell Counting<br>Configuration Register   | (0x102) | Specifies the type of cells counted in per-VC counts. See the Data Sheet [1] for details. |

| Per-PHY Counter<br>Configuration Register | (0x1A0) | Specifies the type of cells counted in per-PHY counts. See the Data Sheet for details.    |

# 6.2.8 Policing Settings

The ATLAS-3200 supports per-VC and per-PHY transmission rate policing. The policing configuration registers are listed in Table 12. These registers should typically be set during initialization, however, they can also be re-configured during Normal Operation state. See the Data Sheet [1] for detailed register descriptions, and see Section 6.3.3 and Section 6.5.7 for per-PHY and per-VC policing information respectively.

ATM cell flows are policed using the Generic Cell Rate Algorithm (GCRA) and packet flows are policed using the Guaranteed Frame Rate (GFR) algorithm.

The ATLAS-3200 has eight pairs of configurations that the per-VC policers select from. Each VC can have up to two per-VC GCRA policing operations active.

The ATLAS-3200 has four global configurations the per-PHY policers select from. Each PHY connection can optionally have one per-PHY GCRA policing operation active.

| Register                                               | Address | Description                         |

|--------------------------------------------------------|---------|-------------------------------------|

| Per-VC Non-Compliant<br>Cell Counting<br>Configuration | 0x130   | Defines the VC non-compliant cells. |

| Connection Policing<br>Configuration 1 & 2             | 0x131   | VC GCRA configurations 1 & 2        |

| Connection Policing<br>Configuration 3 & 4             | 0x132   | VC GCRA configurations 3 & 4        |

Table 12

- Registers for Policing Configuration

ATLAS-3200 PROGRAMMER'S GUIDE

| Register                                                | Address | Description                          |

|---------------------------------------------------------|---------|--------------------------------------|

| Connection Policing<br>Configuration 5 & 6              | 0x133   | VC GCRA configurations 5 & 6         |

| Connection Policing<br>Configuration 7 & 8              | 0x134   | VC GCRA configurations 7 & 8         |

| PHY Policing<br>Configuration                           | 0x142   | PHY GCRA configurations 1, 2, 3 & 4  |

| Per-PHY Non-Compliant<br>Cell Counting<br>Configuration | 0x143   | Defines the PHY non-compliant cells. |

#### 6.2.9 OAM Settings

Operations and Maintenance (OAM) operation is controlled by global configuration settings, per-VC configuration settings, and per-Performance Management settings. During initialization or at run-time the global OAM configurations can be set to their desired values. See Section 6.8 OAM Cell Processing for details on the global OAM configuration settings.

#### 6.2.10 Search Key Settings

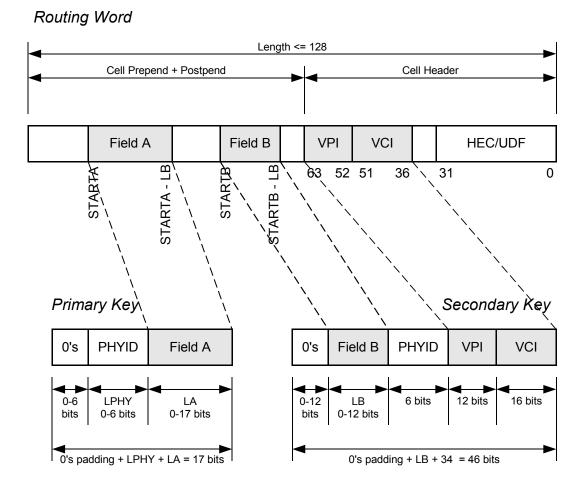

The Search Key settings that should be configured are contained in the register listed in Table 13. See section 6.7 Virtual Connection Search Tree Modifying for further information.

| Table 13 | - Registers | for Search | Key Co | nfiguration |

|----------|-------------|------------|--------|-------------|

|----------|-------------|------------|--------|-------------|

| Register                                | Address | Description                                                      |

|-----------------------------------------|---------|------------------------------------------------------------------|

| Search Engine<br>Configuration Register | 0x10B   | Specifies construction of the Primary and Secondary Search keys. |

#### 6.2.11 Interrupt Settings

After a reset all interrupts are disabled by default. While the ATLAS-3200 is in standby state no interrupts will be generated. Enable the desired interrupts while in Standby state and once the Normal Operation state is entered they will become active. See section 6.10 Interrupt Handling for interrupt information.

#### 6.2.12 VC Table Settings

The VC Table can be modified during Normal Operation state as connections are added and removed, however the VC Table Maximum Index Register (0x110) is a control register that should be set during initialization. This register holds the maximum VC Table address (VCRA[15:0]) and is used by the background processes of the VC Table. This should be set to the maximum address supported by the external SRAM. To ensure proper operation it is important that the VC Table Maximum Index Register not be set to an address greater than that supported by the external SRAM.

**NOTE**: For proper OAM processing the VC Table Maximum Index Register must never be set to zero.

# 6.3 Physical Connection Adding

This section is a guide to programming the routines to add a physical connection to the ATLAS-3200. After the ATLAS-3200 has been initialized, the routines to add physical connections will typically be run once to establish connections to the attached hardware. A physical connection can either be configured to transmit ATM cells or packets.

Adding a physical connection involves configuring four components: Physical ID Mapping, Per-PHY Policing, Scalable Data Queues, and Polling and Servicing Calendars. The general programming algorithm and descriptions of the configuration settings for each of those components are discussed in the sections below.

# 6.3.1 Algorithm

The algorithm to add a physical connection for **ATM cell transmission** is as follows:

- 1. Ensure that this PHY's ProcessPHY bit in the Per-PHY Processing Enable Register (0x105 or 0x106) is set to logic 1.

- 2. Configure the physical ID mapping. (See Section 6.3.2 for settings.)

- 3. Set the per-PHY policing options. (See Section 6.3.3 for settings.)

- 4. Disable and flush the physical connection's FIFO in the Bypass SDQ. To do this perform an indirect write to the PHY's Bypass SDQ entry with the ENABLE bit in the Bypass SDQ Indirect Configuration Register set to logic 0 and the FLUSH bit set to logic 1

- 5. Activate the physical connection's FIFO in the Output SDQ by allocating the location and size of the FIFO. (See Section 6.3.4 for settings.)

- 6. If the output interface uses a polling and servicing calendar in the current operating mode, update the appropriate Polling and Servicing Calendar to include this physical ID. (See Section 6.3.5 for settings.)

- 7. Activate the physical connection's FIFO in the Input SDQ by allocating the location and size of the FIFO. (See Section 6.3.4 for settings.)

- 8. If the input interface uses a polling and servicing calendar in the current operating mode, update the appropriate Polling and Servicing Calendar to

ATLAS-3200 PROGRAMMER'S GUIDE

include this physical ID. The Calendars should only be changed while the Cell Processor is in STANDBY mode. (See Section 6.3.5 for settings.)

The algorithm to add a physical connection for **packet transmission** is as follows:

- 1. Configure the physical ID mapping. (See Section 6.3.2 for settings.)

- Disable the physical connection's FIFOs in the Input and Output SDQs. To do this perform indirect writes to the PHY's Input and Output SDQ entries with the ENABLE bit in the Input and Output SDQ Indirect Configuration Registers set to logic 0 and the FLUSH bit set to logic 1. (See Section 6.3.4 for settings.)

- 3. Activate the physical connection's FIFO in the Bypass SDQ by allocating the location and size of the FIFO. (See Section 6.3.4 for settings.)

- 4. If the output interface uses a polling and servicing calendar in the current operating mode, update the appropriate Polling and Servicing Calendar to include this physical ID. The Calendars should only be changed while the Cell Processor is in STANDBY mode. (See Section 6.3.5 for settings.)

#### 6.3.2 Physical ID Mapping Settings

The RxLink and TxLink blocks can remap the physcial ID's (PHY IDs) of the incoming data flows to arbitrary PHY IDs. The remapped PHY IDs are used by all downstream ATLAS-3200 internal components and external devices. See Figure 2 to determine the downstream components from the RxLink and TxLink blocks. The PHY ID mapping tables contain one entry for each of the 48 possible physical devices and are accessed through indirect registers. By default after a reset each entry maps the external PHY ID to its identical PHY ID.

See section 7.6 PHY ID Mapping Table Interfacing for details on programming the PHY ID mapping tables using the indirect access registers.

#### 6.3.3 Per-PHY Policing Settings

The ATLAS-3200 supports one GCRA policing operation on each of the fourty eight physical connections (PHYs). Per-PHY policing is active for a given PHY when its corresponding bit is set in its PHY Policing Enable register. Per-PHY policing is performed on the cumulative cell flow of all VC's on the PHY that have the PHY Police bit in the Policing Configuration field of their VC Table Record set. For each VC, the PHYID[5:0] field in its VC Linkage Table Record determines which of the 48 PHY policing instances is addressed.

ATLAS-3200 PROGRAMMER'S GUIDE

The PHY policing operations share four global GCRA configurations in the PHY Policing Configuration Register (0x142). When policing is enabled for a given PHY one of the four per-PHY GCRA configurations must be selected.

The policing configuration for each PHY is stored in internal RAM that is programmed indirectly through the PHY Policing Address Access Control Register and the PHY Policing RAM Data registers. See Section 7.7 PHY Polcing RAM Interfacing for the programming algorithms using the indirect registers.

All the registers related to per-PHY policing are listed in Table 14.

| Register                                             | Address                                | Description                                                                                                                                                |

|------------------------------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PHY Policing Enable 1                                | 0x140                                  | Policing enable bits for physical connections 0 to 31.                                                                                                     |

| PHY Policing Enable 2                                | 0x141                                  | Policing enable bits for physical connections 31 to 47.                                                                                                    |

| PHY Policing Configuration                           | 0x142                                  | PHY GCRA configurations 1,2,3,<br>and 4. Each PHY policing<br>selects one of these<br>configurations. This will typically<br>be set during initialization. |